Hi,

My customer is facing the memory effect.

Could you tell me following thing to solve it?

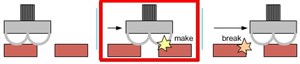

Which is the switch timing of MUX for ADS1120, "break before make" or"make before break"?

If it is "make before break", how long is channels connected?

Thanks and Regards,

Kuramochi