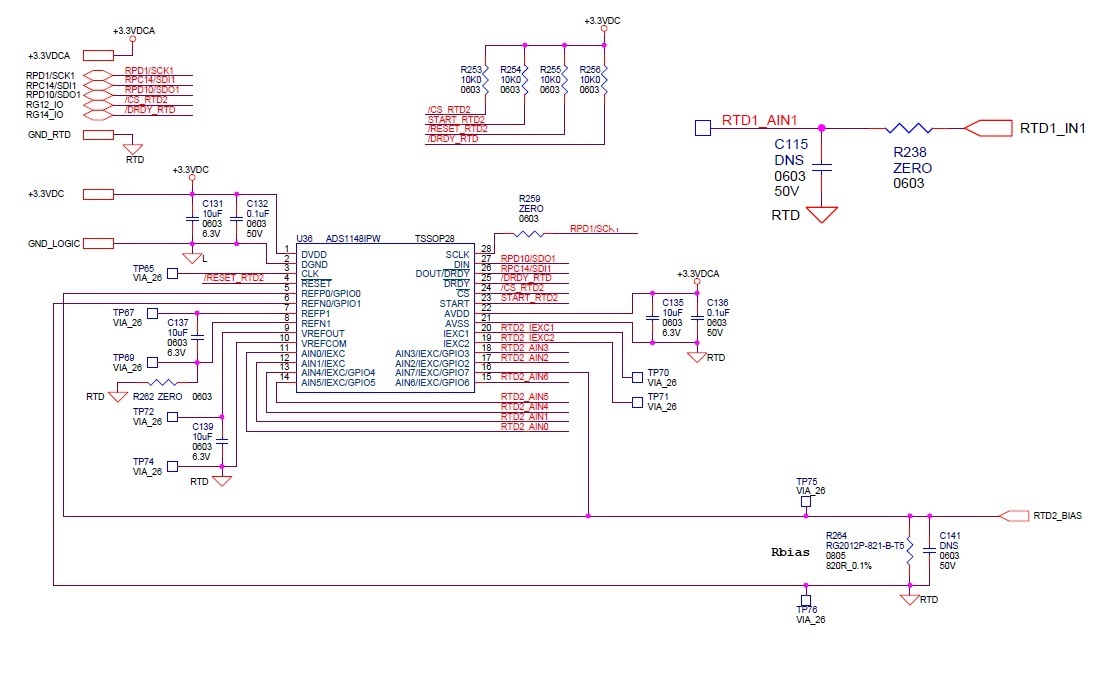

We are using ADS1148, 2 wire configuration. We are using 1k pot to simulate the RTD.

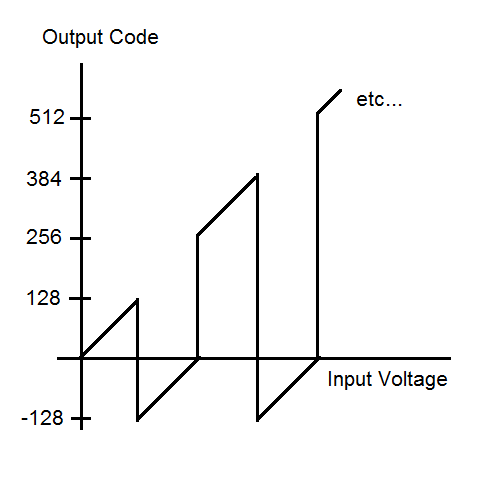

Our issue is: We are getting good readings for 1-100 ohm. Above 100 ohms, we are are getting negative values (65555). If we keep increasing the resistance, above 300 we are getting good readings. What would be the possible cause?

Thank you.