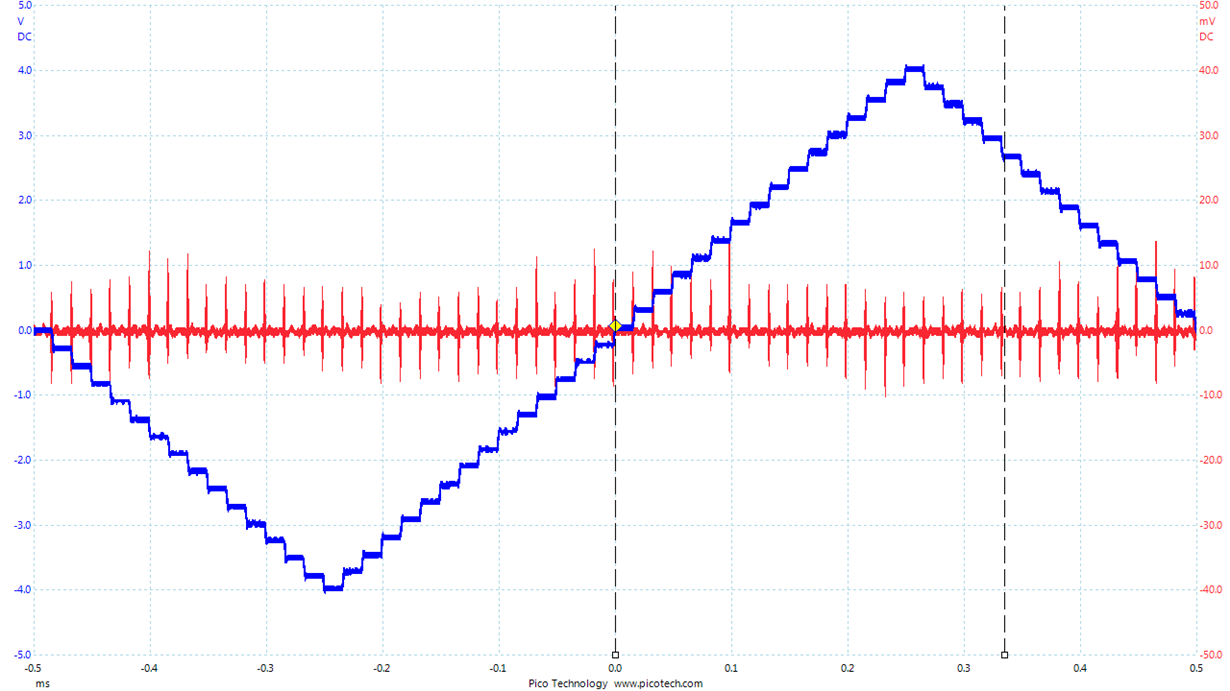

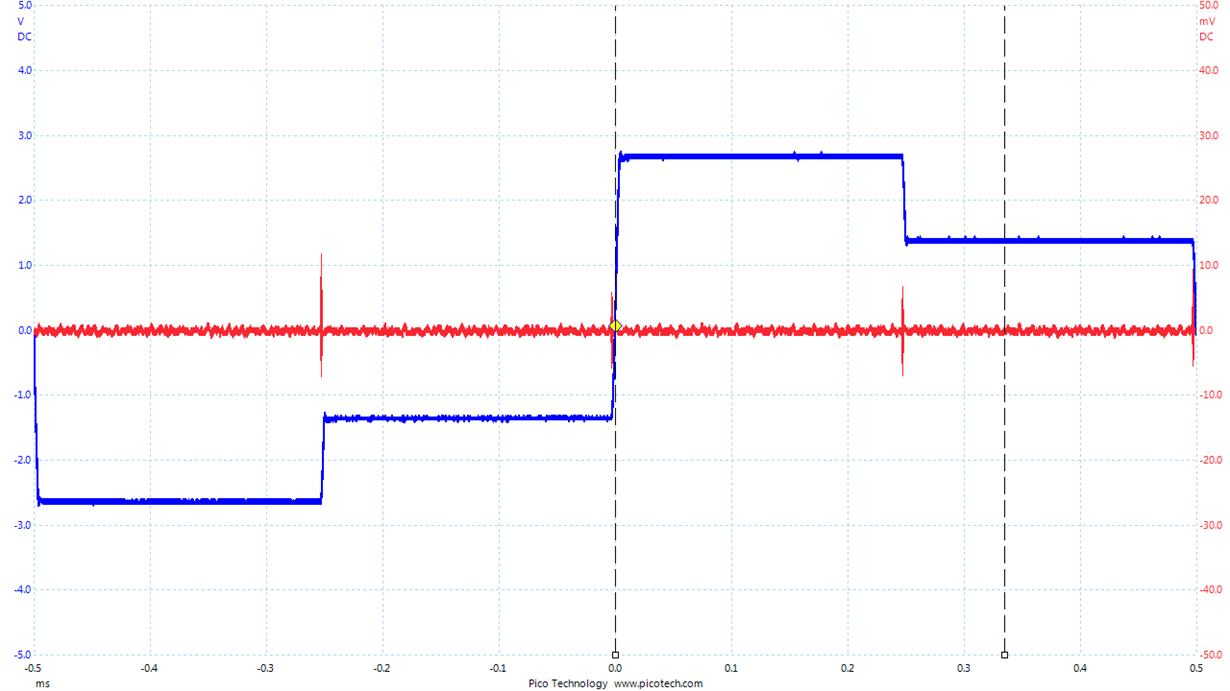

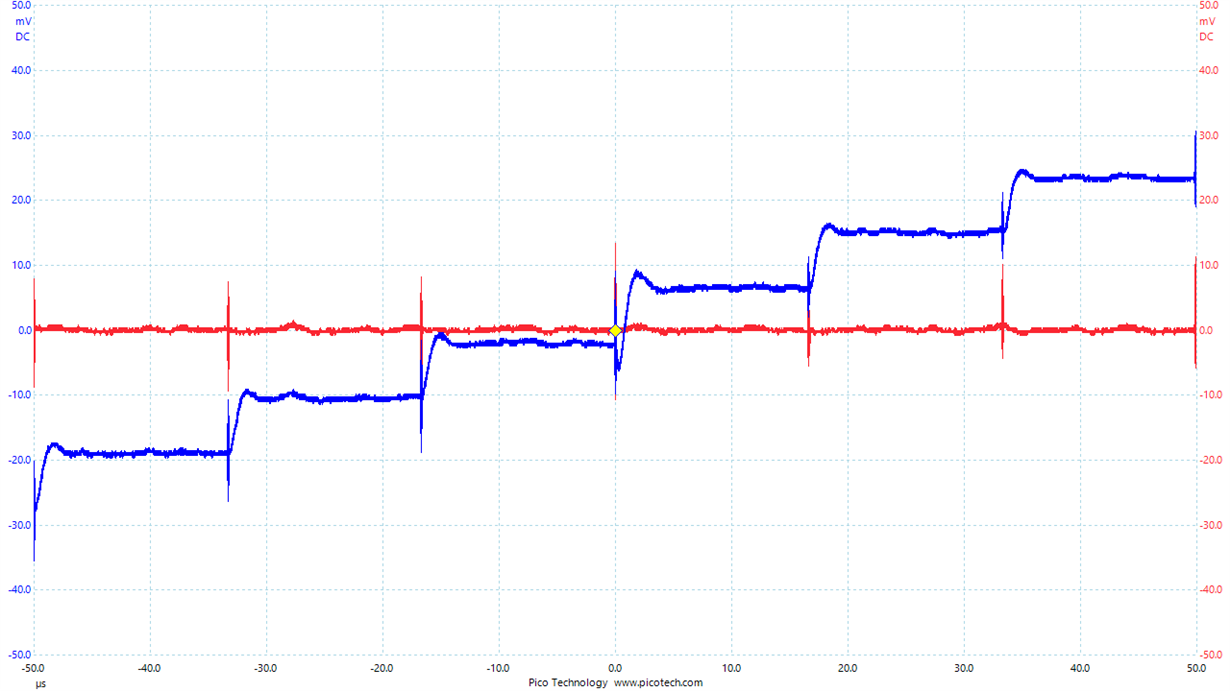

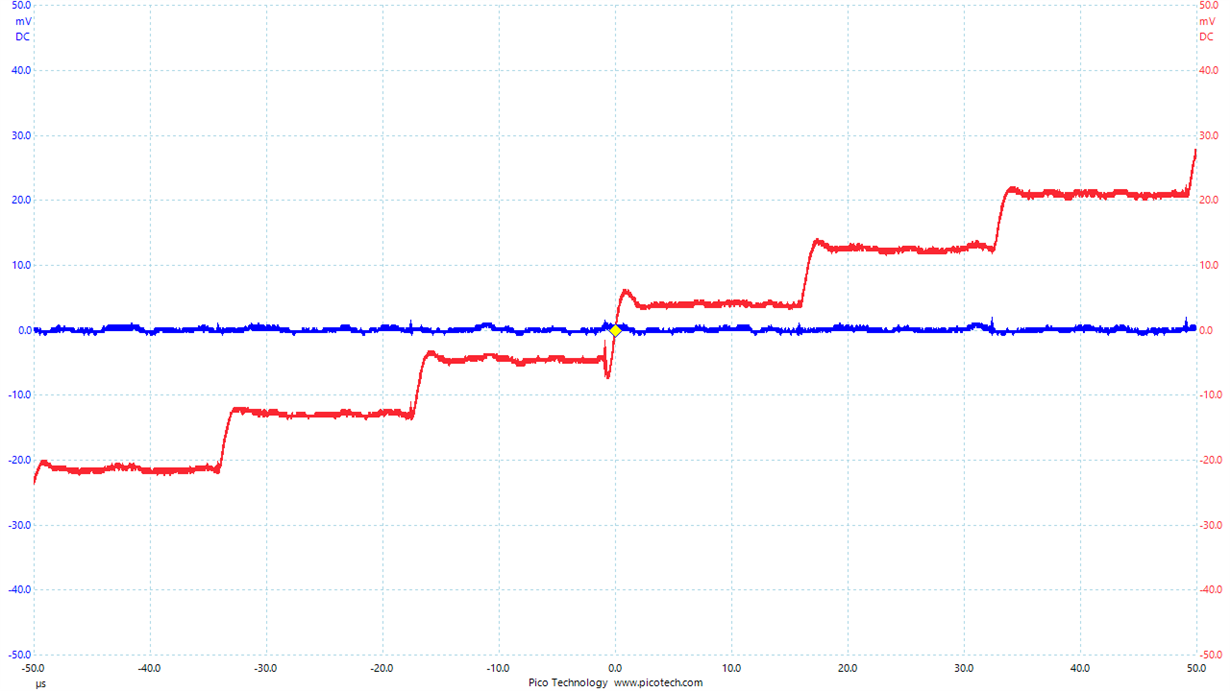

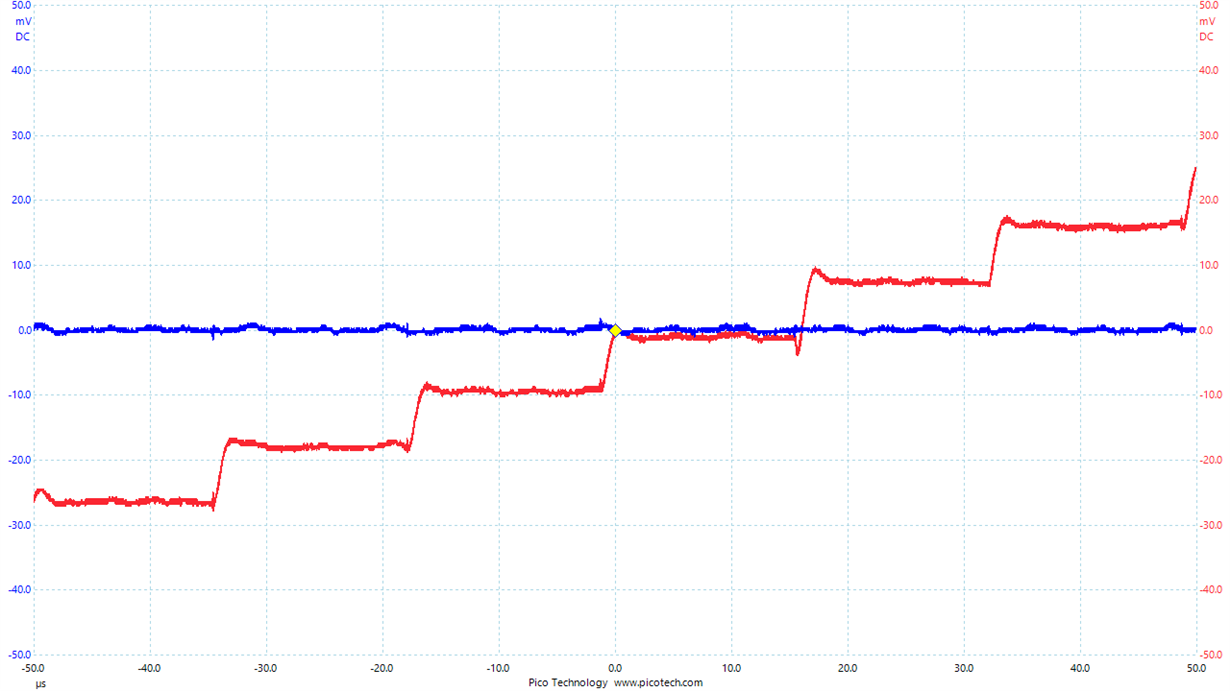

I'm seeing some sort of digital signal embedded in the analog signal of the DAC8822. In the figures attached, the blue and red are the 2 channels. The red channel has the same digital code being set while the blue is being changed. The +/-10mV spikes are happening only when the LDAC signal is toggled, corresponding to the changing analog values on the blue channel. The 2 figures are at different update rates, showing that the spikes correlate to the update rate. Are the spikes supposed to be there, or is there a way to get rid of them by proper design?

Any help would be appreciated.