What if happen if we set IS=1 to enable data capture on I channel, but we set IQ_CAPT =1 in FPGA to enable capture on both I and Q channel?

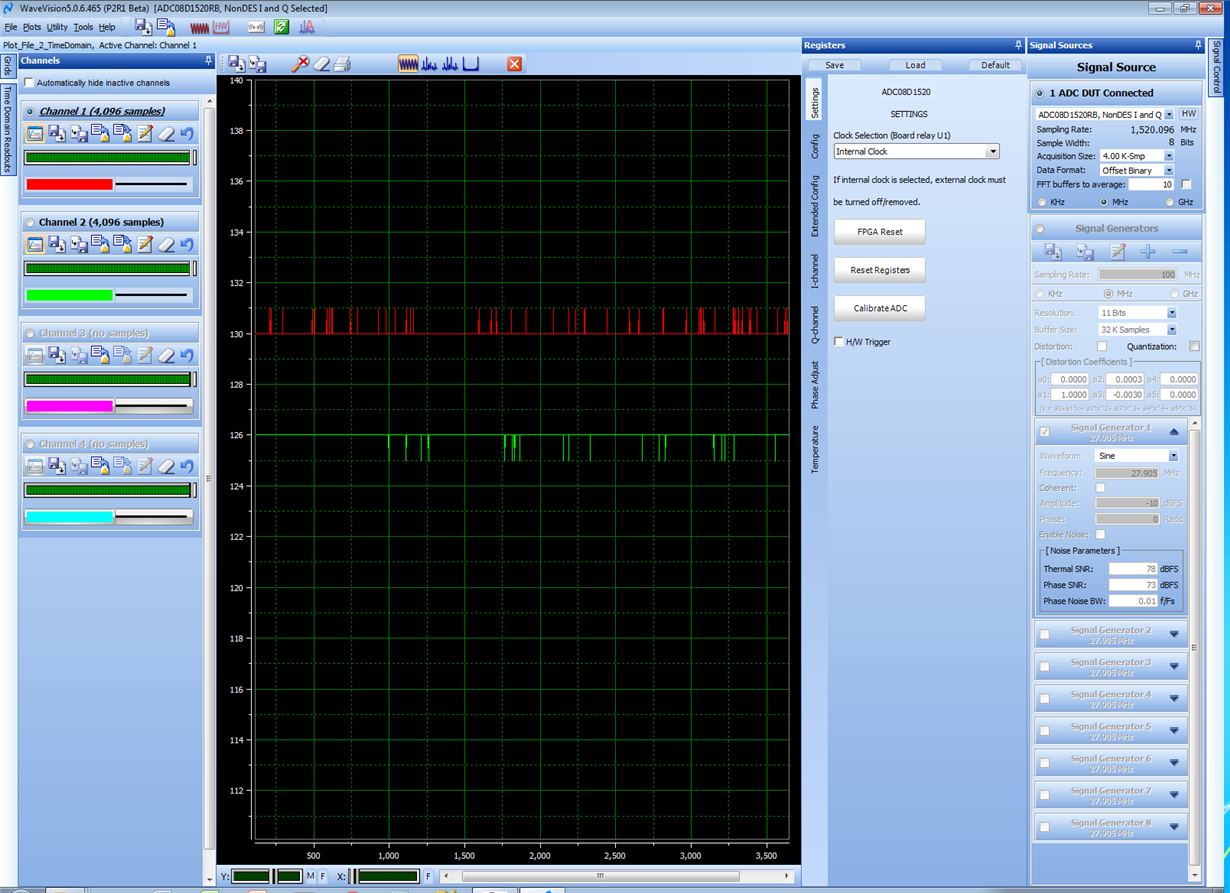

We noticed that even IQ_CAPT is setting as 1, only data is observed on I channel.

Anyone could share their thoughts?

Thanks.

-Bridget