Hi,

I have encountered the below issues during evaluation of ADC12J4000. The ADC12j4000EVM

is connected to TSW14J56, using 4GHz external clock source , 2GHz to

LMKCLK and bypass mode. All input and clock are connected with filters.

1. I keep getting "read DDR to file timed out error" when capturing the data. I

have click on the "Instrument Options>Reset Board". i also tried the CPU reset button on board. the error still appears frequently.

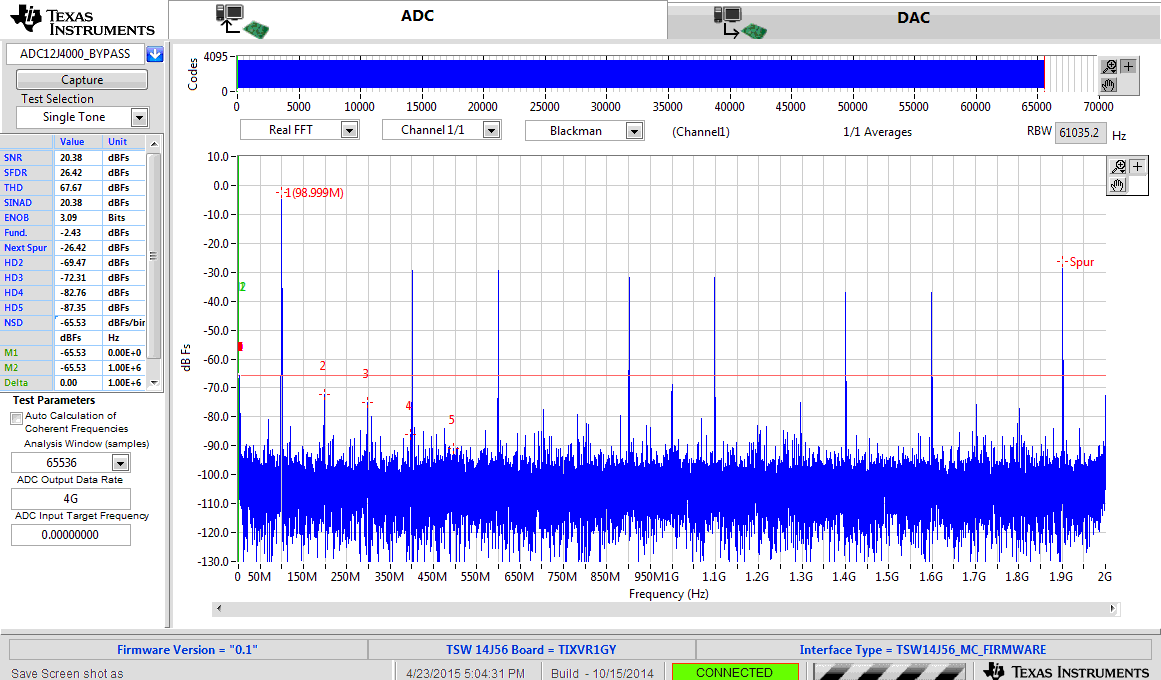

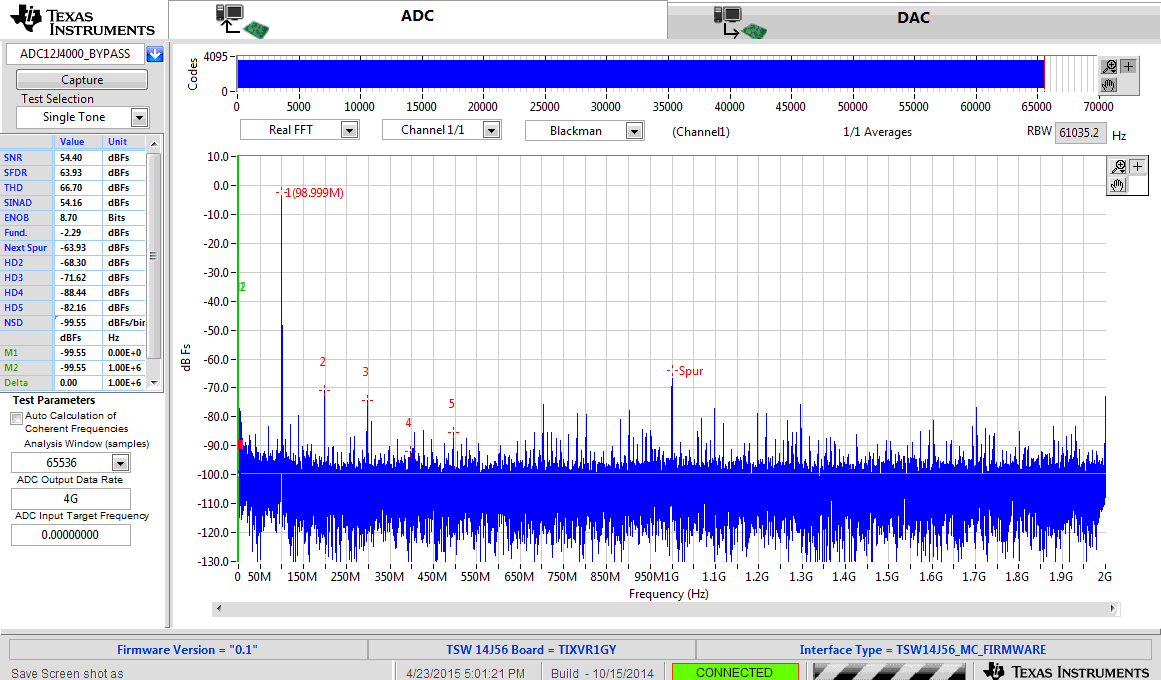

2. when testing at eg. input frequency of 99 MHZ and 4GHz clk rate, i sometimes get many

high spurs ( as high as 30dB from fund) and sometimes good results. please see attached. what is causing the high spurs?

High Spurs captured:

Good capture: