We are experiencing some problems using a ads1247. It's not giving us reliable results.

We spend quite some time with code snippets from the TI forums, but no result yet.

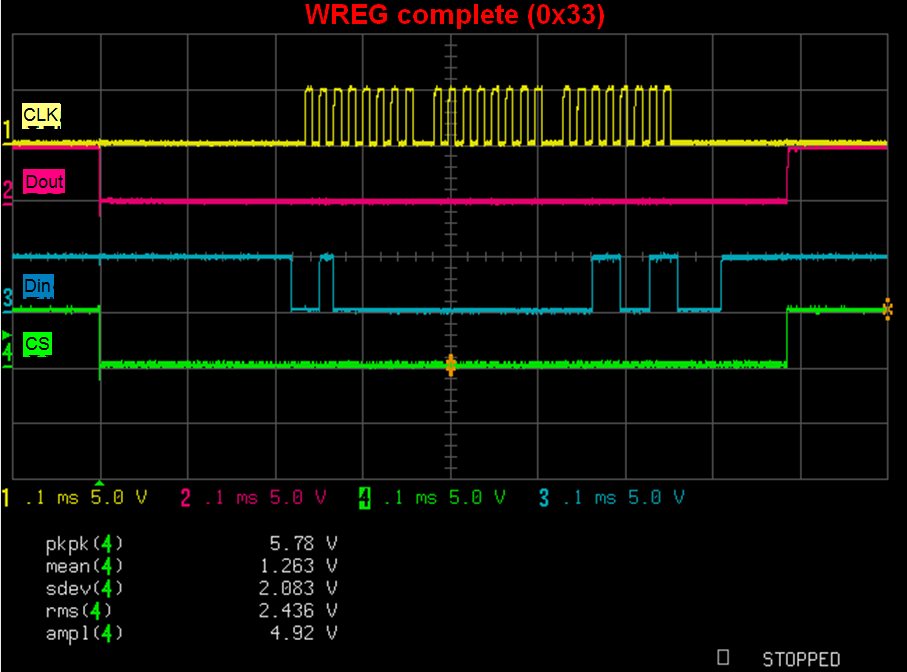

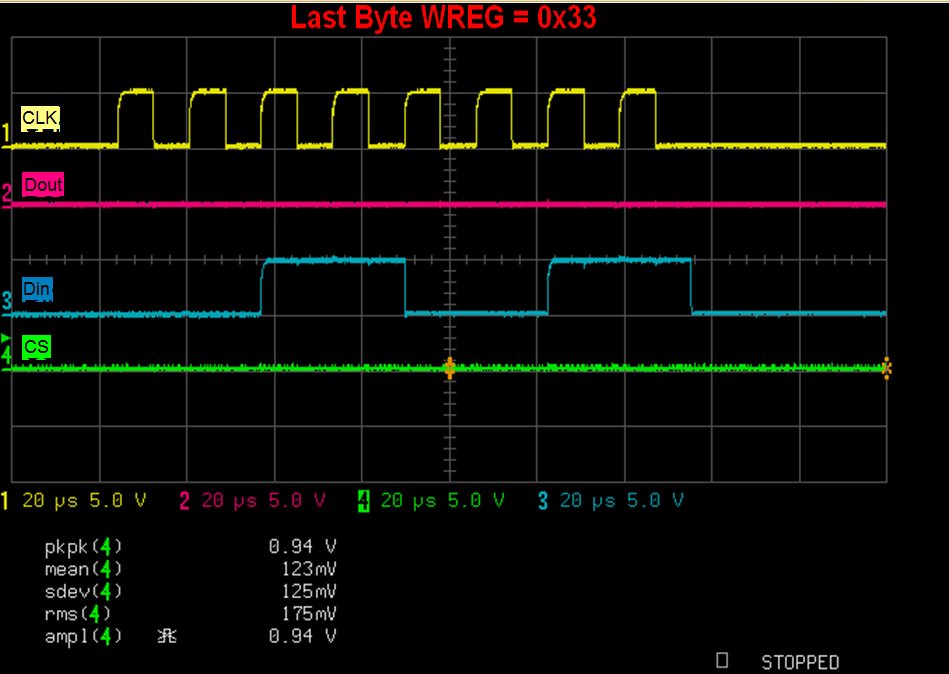

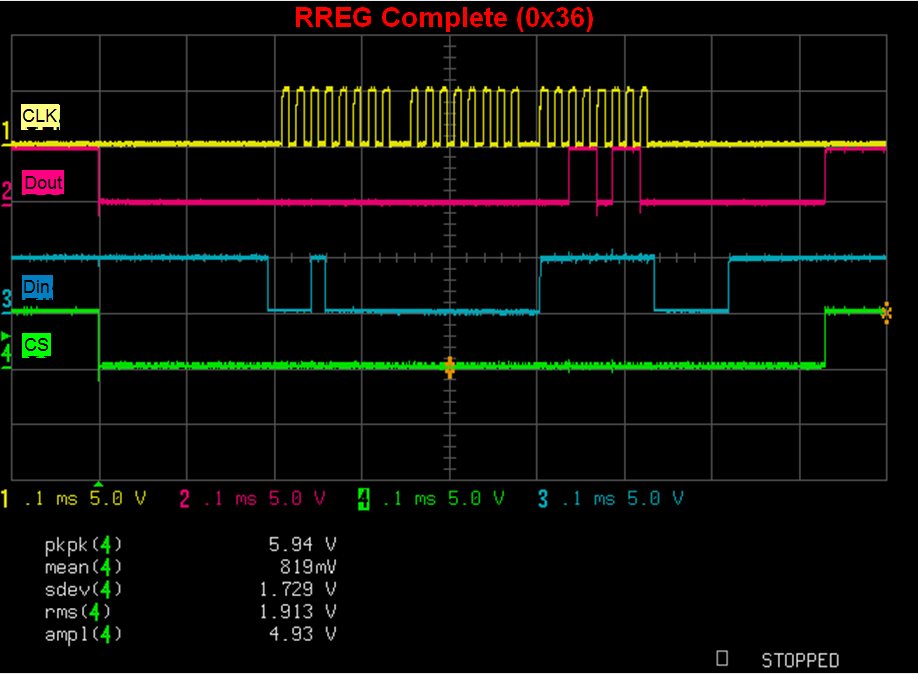

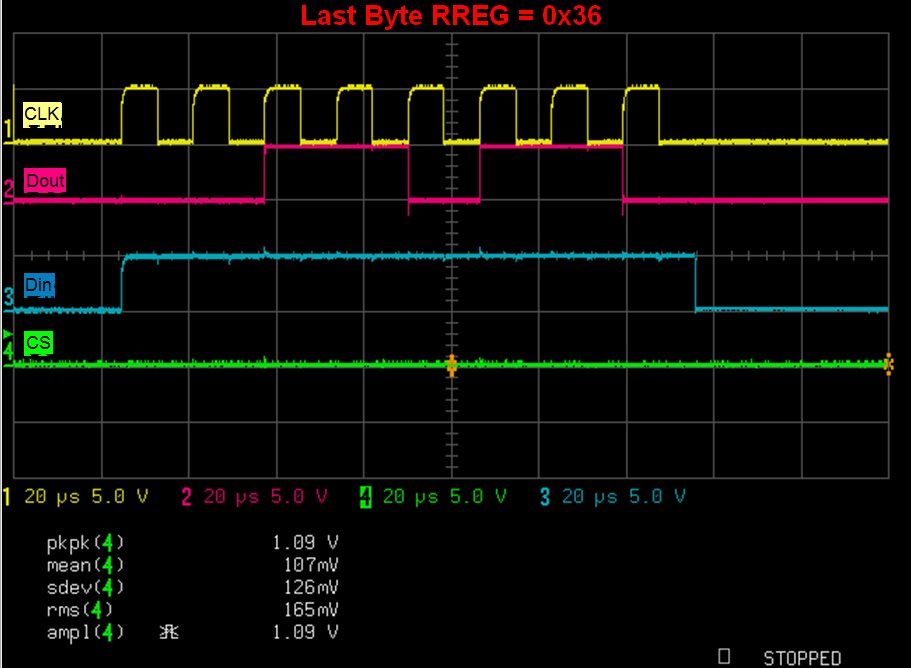

Debugging the issue, we first tried to read the internal temperature diode. But doing that showed that even reading back the registers with the RREG command does not work reliable. And furthermore the RDATA results do not make sense.

Sometimes we read back the correct result, but most of the times not.

We use the following code to drive the chip.

def ads1247_smalltest(spi):

"""Basic test sequence to test ads1247

"""

CS = PIN_LOCKIN_CS3

RDY = PIN_DAT_RDY3

START = PIN_START3

spi.mode = 0b01

GPIO.output(START, True)

GPIO.output(PIN_RESET, False)

time.sleep(0.001) # >4 cycles

GPIO.output(PIN_RESET, True)

time.sleep(0.002) # >0.6ms

GPIO.output(CS, False)

spi.xfer2([0x6]) # RESET

time.sleep(0.002) # 0.6ms

spi.xfer2([0x16]) # SDATAC

GPIO.wait_for_edge(RDY, GPIO.FALLING)

spi.xfer2([0xff, 0xff, 0xff]) # dummy read

# MUX0, VBAS, MUX1, SYS0

spi.xfer2([0x40, 0, 0x1])

spi.xfer2([0x41, 0, 0x0])

spi.xfer2([0x42, 0, 0x33]) # internal temp

spi.xfer2([0x43, 0, 0x4F])

time.sleep(1)

# read back the registers (they do not read back correctly !)

data = spi.xfer2([0x22, 0, 0xff])

print "MUX1 %x" % data[2]

data = spi.xfer2([0x22, 0, 0xff])

print "MUX1 %x" % data[2]

data = spi.xfer2([0x20, 0, 0xff])

print "MUX0 %x" % data[2]

data = spi.xfer2([0x20, 0, 0xff])

print "MUX0 %x" % data[2]

# IDAC0, IDAC1

spi.xfer2([0x4a, 0, 0x06])

spi.xfer2([0x4b, 0, 0x1])

while True:

GPIO.wait_for_edge(RDY, GPIO.FALLING)

data = spi.xfer2([0x12, 0xff, 0xff, 0xff])

result = data[1] << 16 | data[2] << 8 | data[3]

print "result %x" % result

GPIO.output(CS, True)

The output is

MUX1 c0 MUX1 81 MUX0 4 MUX0 0 result ff8020 result 408102

You see, i read back mux1 with different values, (both not the ones we actually set).

Our digital connection (SPI) seems somewhat ok though, we are able to blink a led via GPIO0 (REFP0).

Anyone having a suggestion how to drive the chip, to measure its internal Temp ?

What we want to accomplish (after we've seen that reading the temp works) is measuring two voltages alternating. (AIN0, AIN1: both compared to AIN3 (connected to GND). Any tips on how to drive this ?

Thanks,

Harm