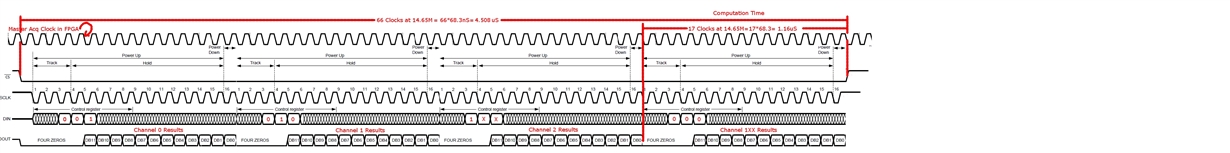

I plan on designing in a ADC128S102 in a sampled data acquisition system. The overall sampling rate is 200 kHz (5 us) and there are 3 signals which must see this 200 kHz rate, and 4 signals which will see 1/4 this rate. The channel sequence I plan on using is 0-1-2-4, 0-1-2-5, 0-1-2-6, and 0-1-2-7, being driven by a 14.65M clock. This gives me 4.5 us conversion time. I set up the following sequence - can anyone tell me if I am close?

Next question - to achieve the 14.65M clock I am dividing a 102.5M clock by 7 which will result in a 3/7 asymtery on the SCLK. This exceeds the data sheet limits of 40/60% - which at 16M are 25 nS and 37.5nS. However since I am reducing the clock frequency from the maximum the minimum high/low times will be 27 nS/41 nS. Is the pecentage high/low regardless of frequency or is it based on minim high/low times?

Next question - to achieve the 14.65M clock I am dividing a 102.5M clock by 7 which will result in a 3/7 asymtery on the SCLK. This exceeds the data sheet limits of 40/60% - which at 16M are 25 nS and 37.5nS. However since I am reducing the clock frequency from the maximum the minimum high/low times will be 27 nS/41 nS. Is the pecentage high/low regardless of frequency or is it based on minim high/low times?