Other Parts Discussed in Thread: ADS1298

Hello

We are using ADS1298 in our product ;

The problem is the AC line interface that distroy completely most the times or add noise to the ECG signal ; Even we have the sigital filters nortch in the DSP side.

May it is the RLD problem ; but we use the values suggested by TI 1.5nF with 1M ohm on the feedback that gives about 106 hz ,

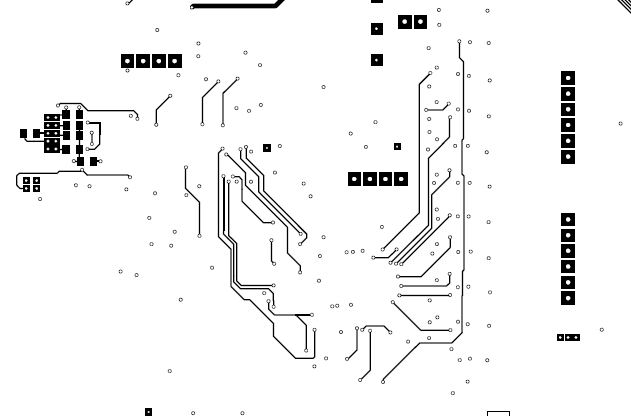

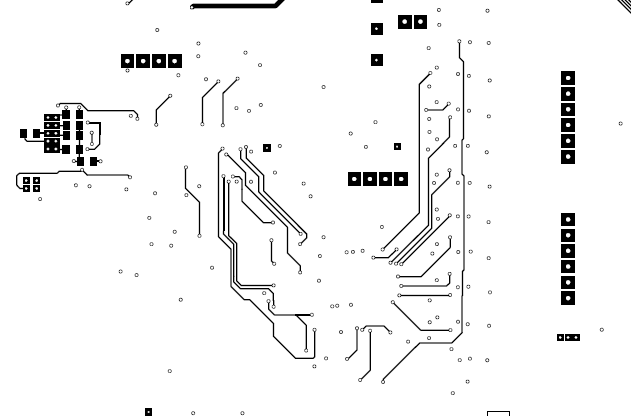

So please could you guide us to solve this problem; here the pictures of the ECG

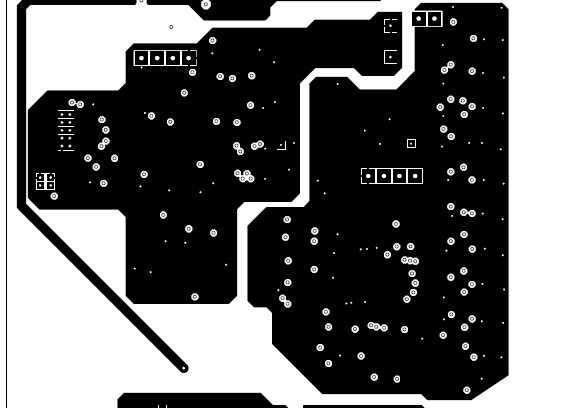

When the device is powered from battery the first picture as you see a good ECG ; but when we power the system from AC ; the ECG is noisy and some times is gone completely ; even we use isolation power between the main board (DSP ) and the analog side ADS1298.

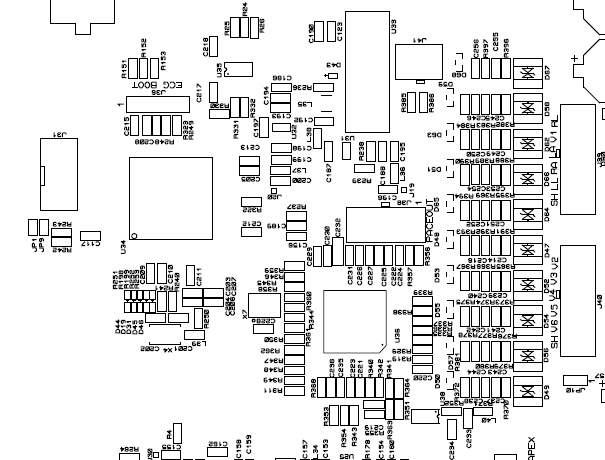

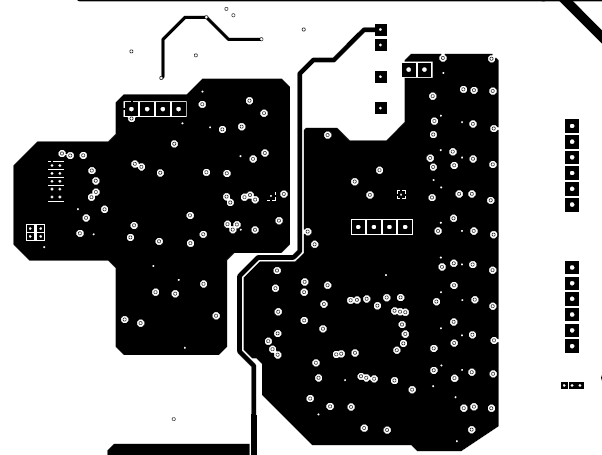

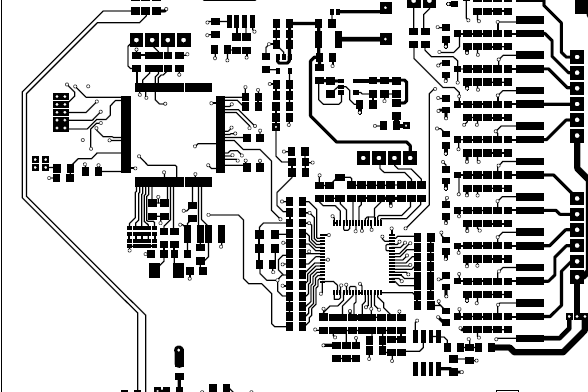

Here our shematics

ads1298.pdfads1298_2.pdfads1298_power.pdf

Thank you ;

Regards