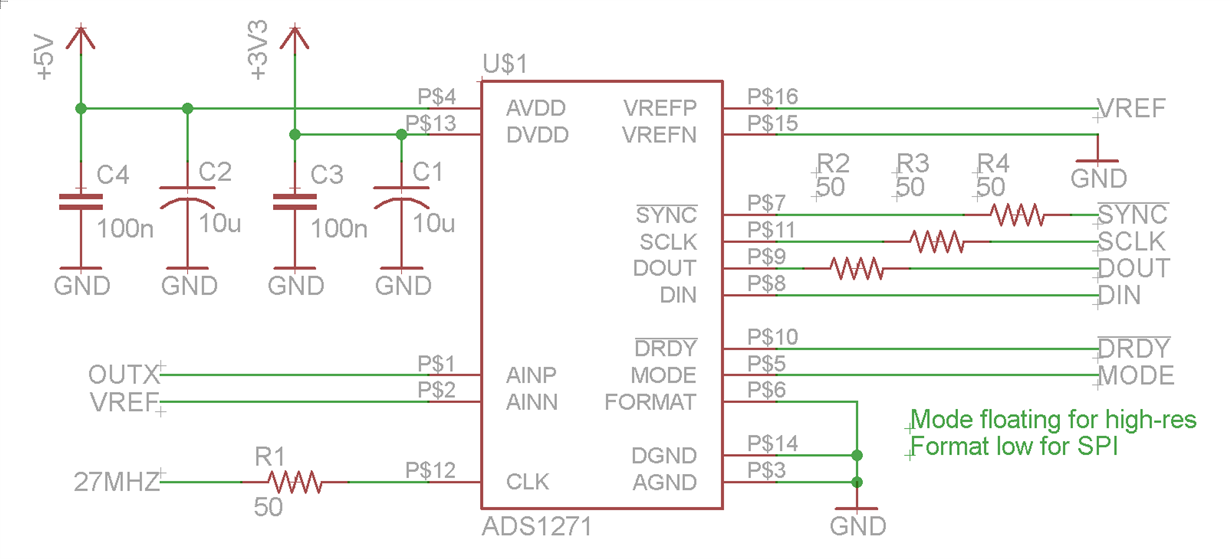

I'm attempting to get data from an ADS1271 converter but the reading is always zero. The ADC is being used in high resolution mode with SPI format.

I'm using the SPI peripheral on an EFM32 microcontroller. My code transmits 0xFE (MSB first) to create a SYNC pulse along with some SCLK cycles at 1MHz.

Based on the datasheet, I thought that DRDY would go high after the SYNC pulse for 512 CLK cycles (~19usec with CLK at 27 MHz) and then DOUT would start shifting the reading out on the falling edges of SCLK. Instead, DRDY goes high for ~36 usec and DOUT goes low for about the same time.

I'm using the center pin of a potentiometer (for testing) as the positive AIN for the ADC which gives a signal between 0 and 5V. Eventually I'll use the output of a difference amplifier with 0 to 5V swing. The negative AIN and the positive VREF are connected to a buffered 2.5V reference.

I've attached screenshots with schematics and logic analyzer output. Here is the code I'm using to talk to the ADC:

do {

/* Data reception from slave */

/* ************************** */

/* Setting up RX interrupt */

SPI1_setupRXInt(receiveBuffer, RXBUFFERSIZE);

/* Receiving data by transmitting dummy data to slave */

USART1_sendBuffer(transmitBuffer, TXBUFFERSIZE);

Delay(100);

/* Clearing the receive buffers */

memset(receiveBuffer, '\0', RXBUFFERSIZE);

} while (1) ;