Hello,

Is there a difference between the Software Reset command and the Reset Pin. I use several ADS131E08 parallel. Sometimes if I power the device one of the ADS131E08 don't react. All the ADS131E08 get the same configuration commands.

1. start external converter clk until the FPGA is initialised (after power up the System 20 Seconds later the FPGA will initialised )

2. Send reset Command

3. wait more then 18 tclks

4. SDATAC

5. Change config Register 1 set 24 bit mode

6. Set RDATAC

7. Set start pin 1 to synchronise the Converters

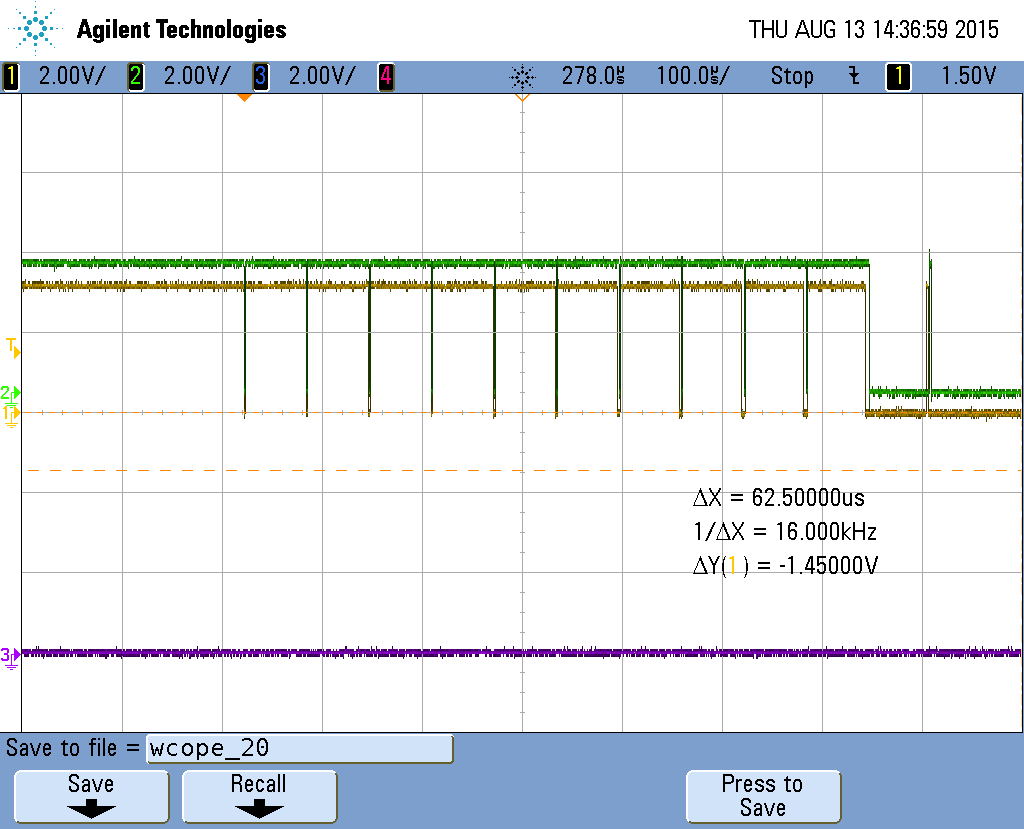

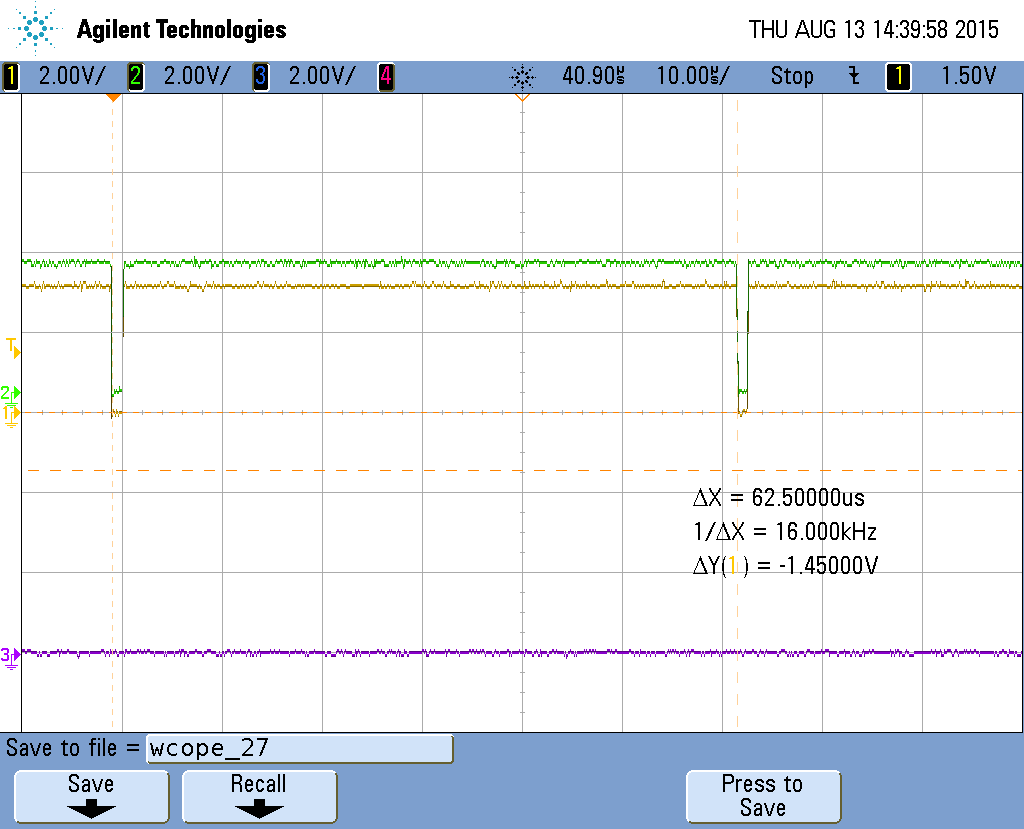

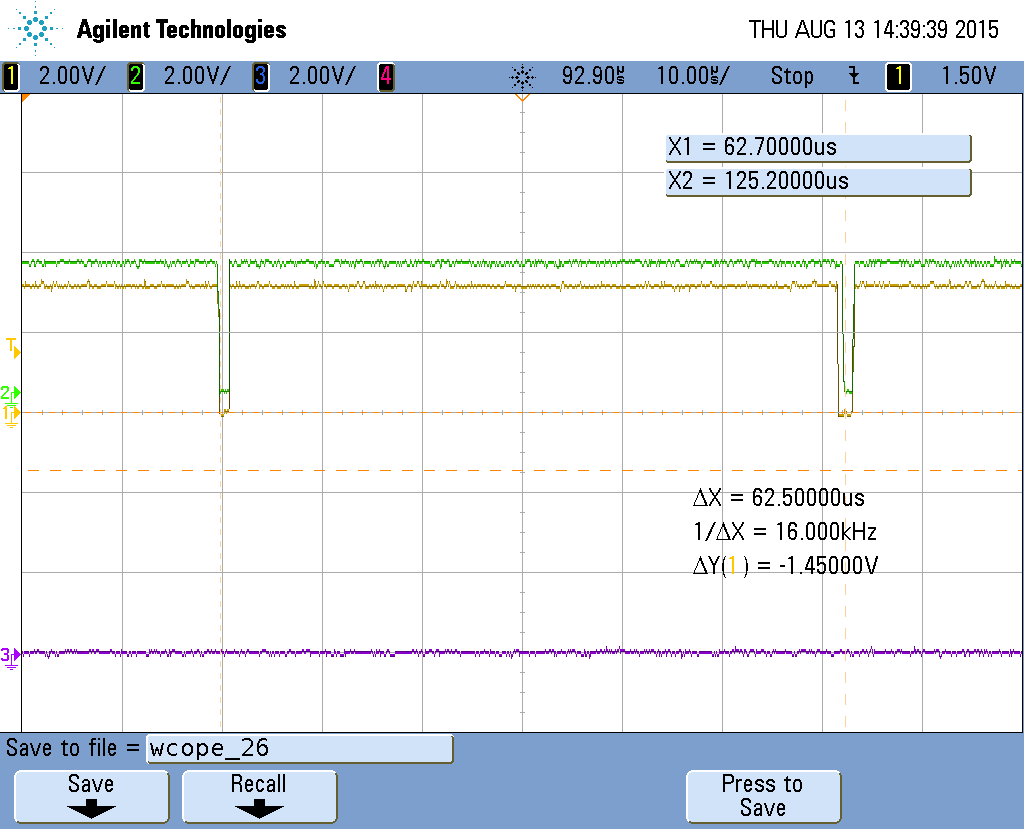

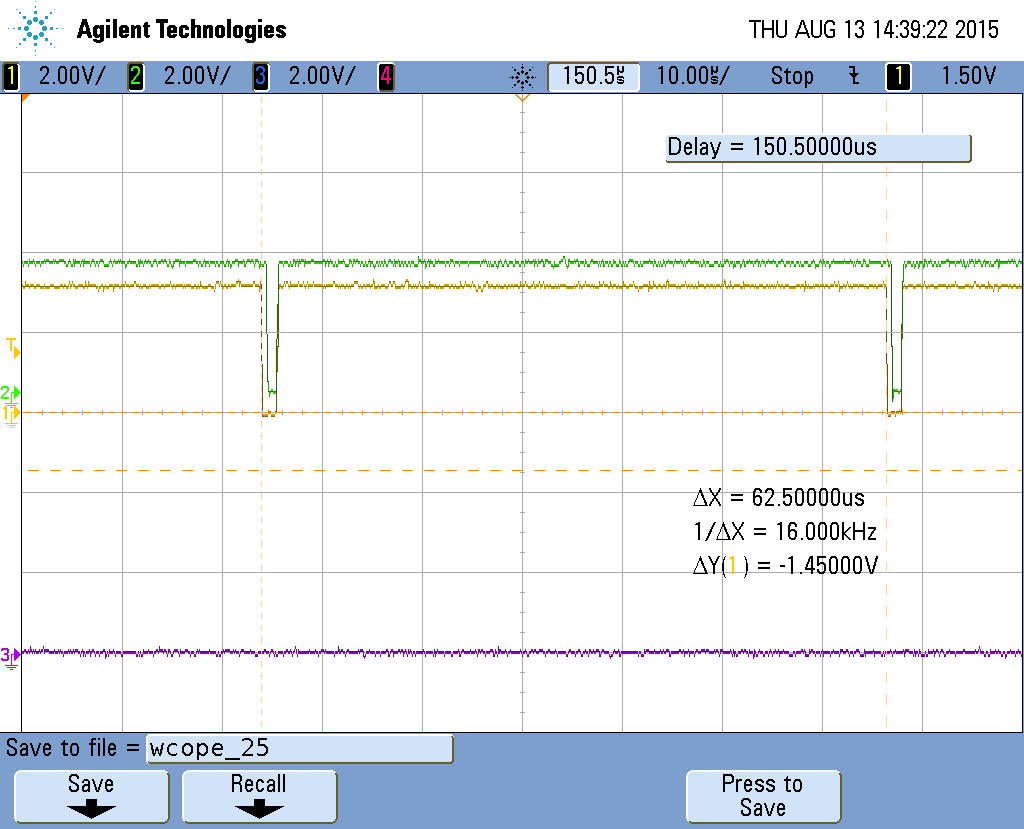

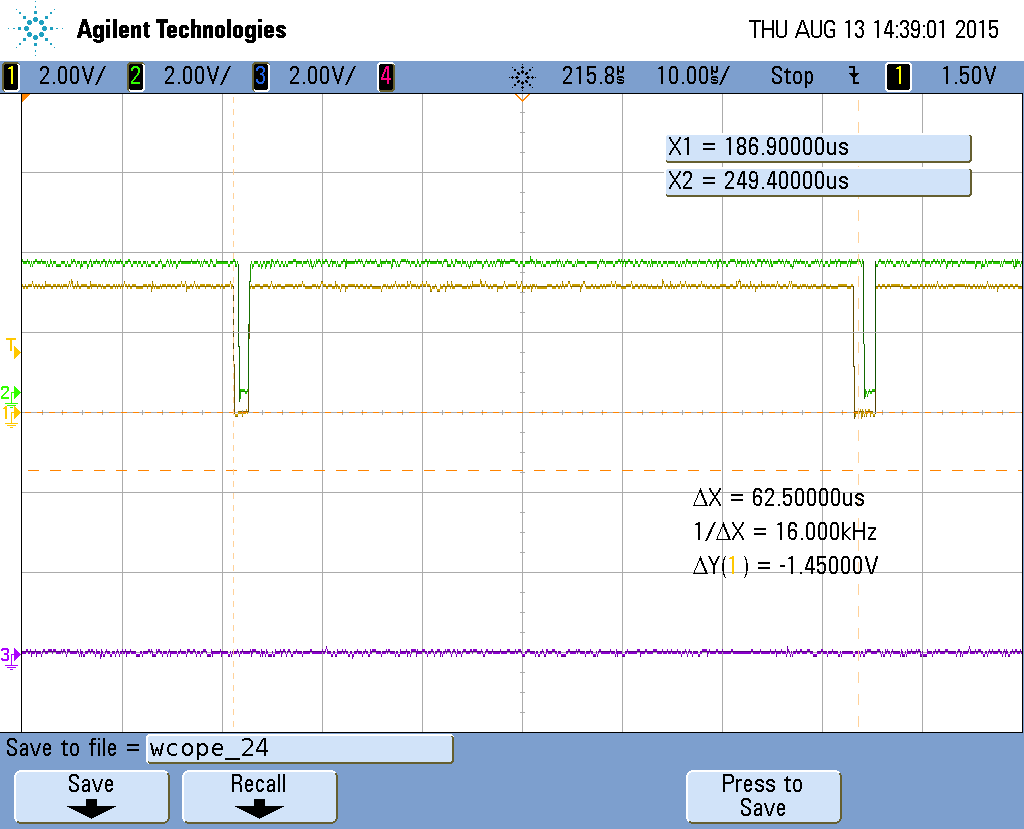

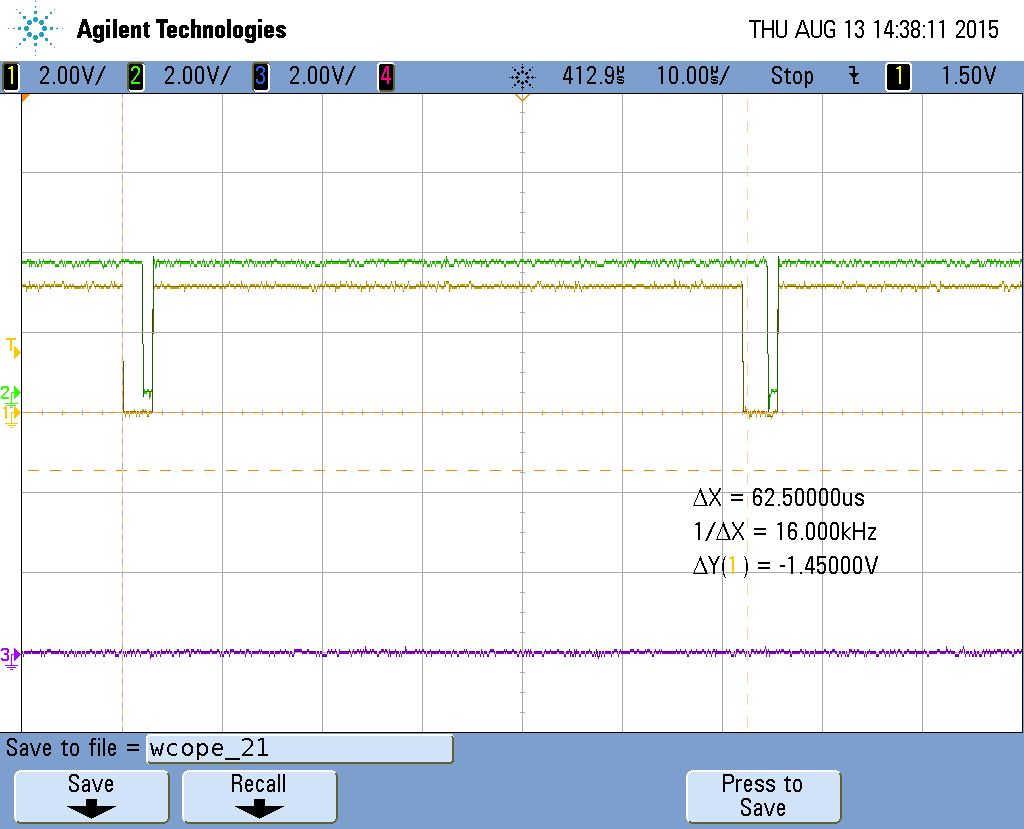

8. Wait for DRDY low on all Converters. In this states happens that the one converter doesn't answer. And this behave is random. That means it is ADS131E08 number one, tow three random too.

After DRDY not react the FPGA try to reinitialise the ADS131E08 again without success.

Can in this Case a the reset Pin help?

The reset pin is at the moment not connected(to connect this is possible, but not provided at the moment) but I should know is the reset pin able to bring the ADS131E08 back to service, even when the ADS131E08 is in a undefined condition.

Best regards

Bernd