Hi all,

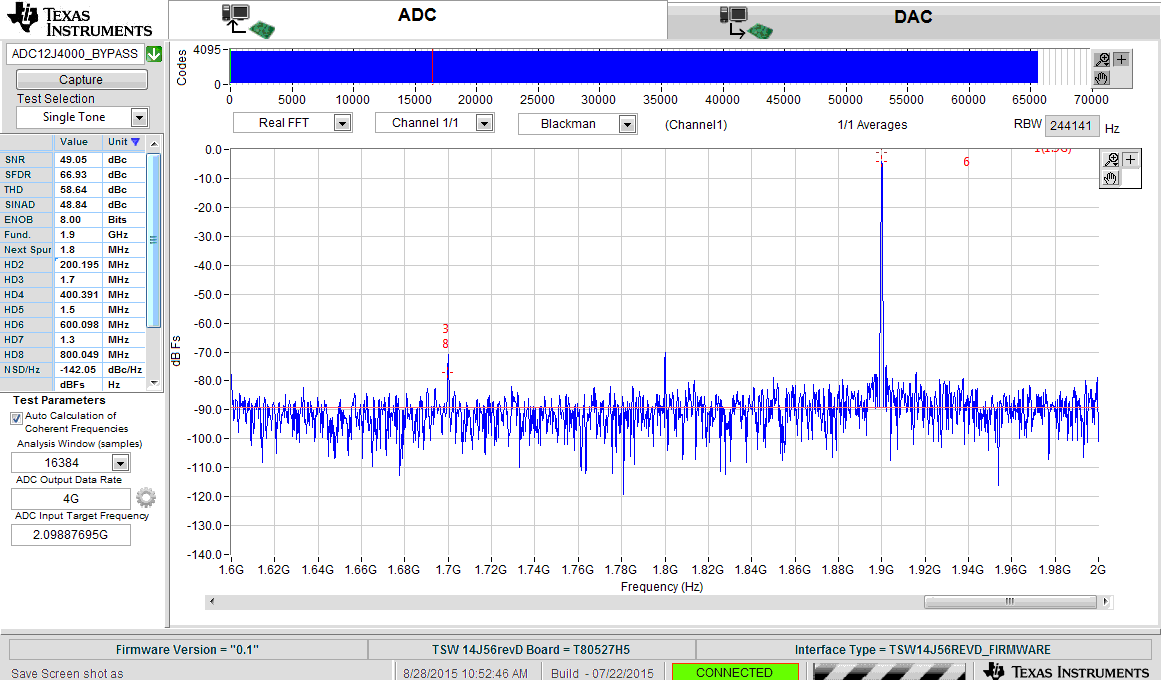

we are using the ADC12J4000 on one of our board (4 ADCs). It behaves globally as expected, except in a small part of the spectrum where the SFDR loose about 10dB.

Did anybody see such behaviours?

I did test with the following sampling frequencies : 3.0, 3.2, 3.4, 3.6, 3.8 and 4.0GHz.

Depending on the sampling frequency, SFDR degradations happens when the carrier is between 80MHZ an 100MHz from Fsampling/2. There are 2 spurious on each side of the carrier which appear when the carrier is in this part of the spectrum.

If I lower the carrier power, then these spurious disappear suddenly when the level goes below between -3.5dBFs and -4dBFs (depending on the ADC).

Moreover, the zone location seems to be proportional to the sampling frequency.

To do the SFDR measurements I removed from the spectrum the signal's harmonics and the interleaving offset spur at Fs/4.

The ADC configuration is as follow:

- enable large signal

- foreground calibration

- disabled background calibration

- enable timing calibration

- carrier level about -1dBFs

regards,

Manuel