Hello,

1). I use DAC5688 in External Clock Mode. the PLLEnable=disabled. PLLSleep = sleep.

Do I still need to concern about the PLL_range and PLL_gain, PLL_m, PLL_n settings?

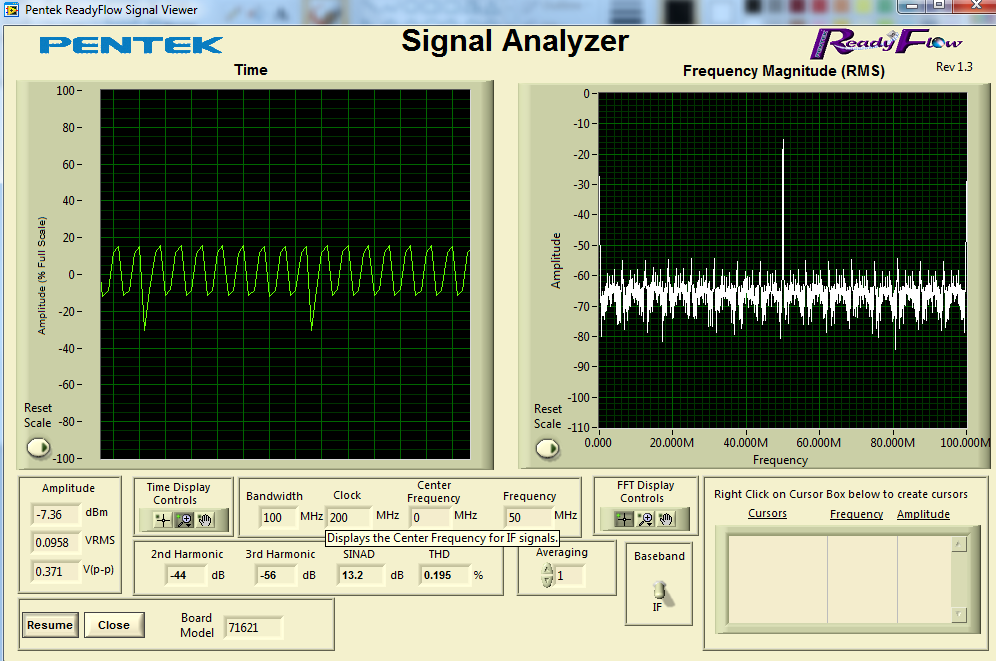

2). My Input clock is 250MHz. If using internal interpolation =1 on the DAC5688 chip, that means the output clock is 250MHz. which exceeded the specified 160MHz Max CLKO output. I saw that the output signals are not continued.  the waveform looks like this. Is it because that the DAC output clock exceeding the 160MHz ?

the waveform looks like this. Is it because that the DAC output clock exceeding the 160MHz ?

Thanks!

Mei guodong