Hi

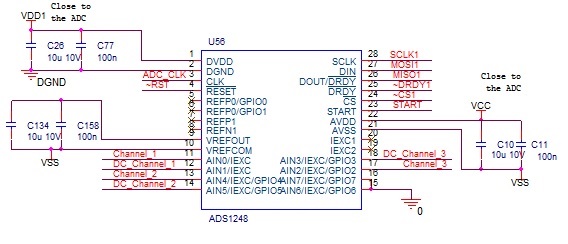

I having problem with series of ADS1248 that used with same code

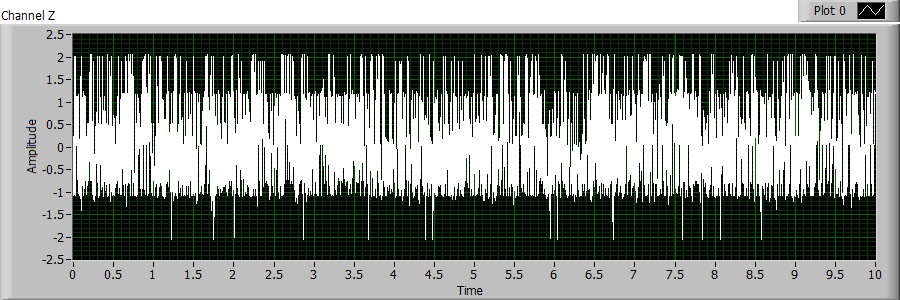

some works and some has greater gain

the code is using accurate external clock to for timing 900Hz in 2000 samples per second

the pseodo code is as follow

in the start of the code i Initializing

RESETn=0

wait 500us

RESETn=1

wait 50ms

START=1

writeSPI(WREG+MUX0)

writeSPI(3)

writeSPI(P_AIN0+N_AIN6) or writeSPI(P_AIN4+N_AIN6) or writeSPI(P_AIN2+N_AIN6) // change sequentially

writeSPI(0)

writeSPI(0x30)

writeSPI(0x0F) //rate: 2000sps gain: 1

then i reading using RREG to verify writing is good

timer at 900Hz trigger interrupt that:

Start=1

wait 1mSec

CSn=0

writeSPI(WREG+MUX0)

writeSPI(3)

writeSPI(P_AIN0+N_AIN6) or writeSPI(P_AIN4+N_AIN6) or writeSPI(P_AIN2+N_AIN6) // change sequentially

writeSPI(0)

writeSPI(0x30)

writeSPI(0x0F) //rate: 2000sps gain: 1

Start=0

CSn=1

wait for DRDYn to go down

CSn=0

writeSPI(RDATA)

readSPI(result[][2])

readSPI(result[][1])

readSPI(result[][0])

CSn=1

I tried many configurations an my final conclusion is that either you have defected series

(working DXXX, not working CXXX)

both bought from digikey

or I am doing something wrong

please help