I'm am looking for a quick turn for a customer I have aggressively supported.

My question is: if I am sampling at say 1200SPS or at the 14.4KSPS is it realistic to measure a low frequency sinusoid (around 1KSPS) with the ADS1259? My guess is yes, but I am guessing that there is a slew rate limitation?

Probably the DR bits set to 5 for 1200SPS, or 0 for 14.4KSPS.

My real question is probably more about aperture window. I am guessing that the window of sampling is smaller at the higher sample rates.

If you look at figure 54, I understand that one, but why would one toss the sample during transition...isn't that what a filter does? Just want to be sure I am not missing something.

At the moment I am just software polling the data-ready bit which is not all that accurate and I suspect I am missing samples due to that polling.

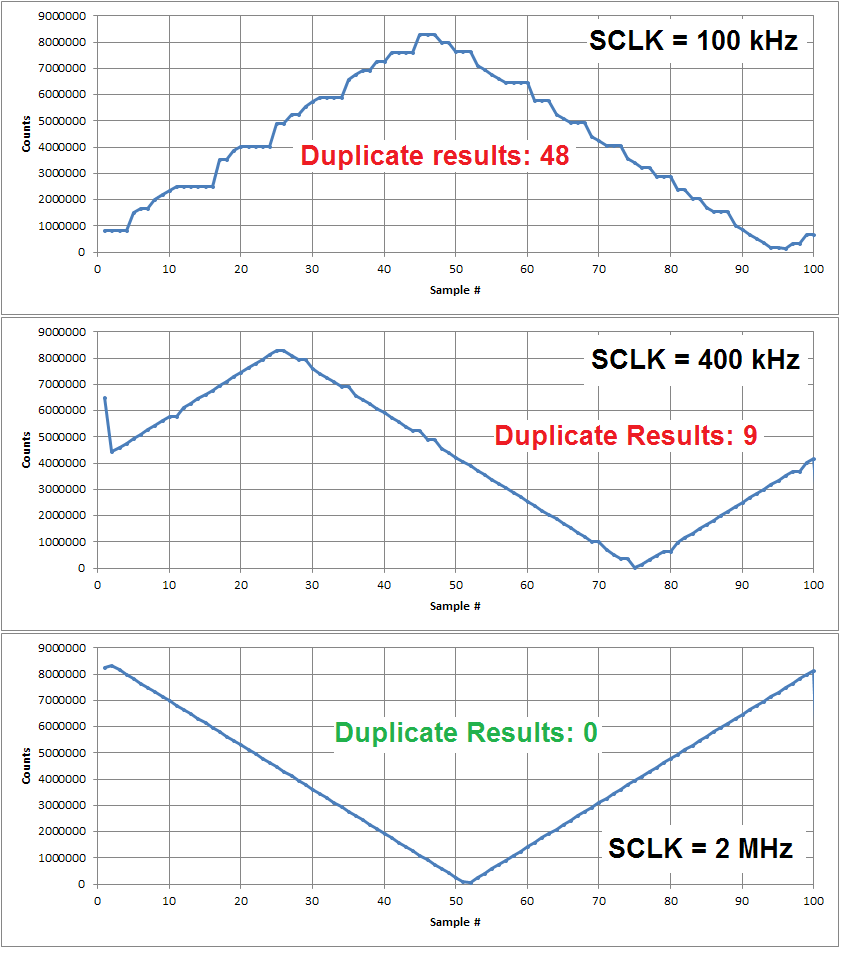

The one peculiar thing I am seeing is that sometimes I get two or three samples that are the exact same value in a row. Even if I run the

ADS1259 with DR=0 (10SPS). In my software I also post a number for each sample indicating whether or not our loop to test for data ready has run at least once (meaning it has detecting data ready inactive), and doing so I still get duplicate values.

Since my software is polling the data ready bit in the ADS1259 register I can understand if we miss a sample here or there. At even the 10SPS data rate every once in a while my software will miss the data ready going inactive.

In the software I am simply getting the ADC value and writing to an array. After 1024 samples, it then writes it all to a file.

I am running the SPI interface clock at 100KHz.

what might cause one to read out duplicate A/D values?