Dear Sir,

May I get an advice on a trouble of ADS42LB69?

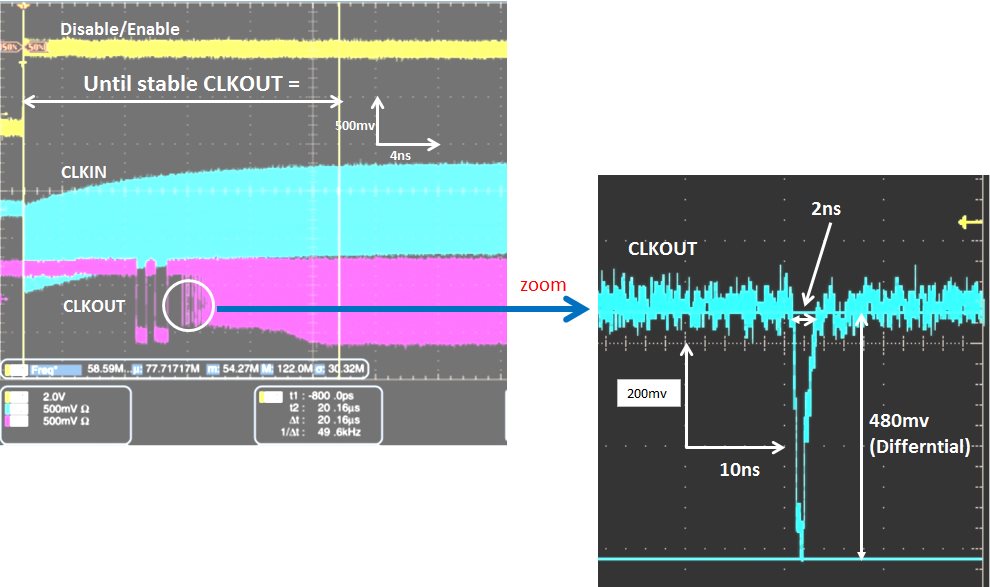

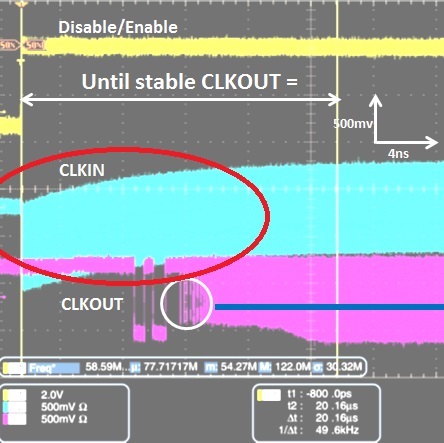

Phenomenon: CLKOUT will not be stable until 20us after CLKIN started

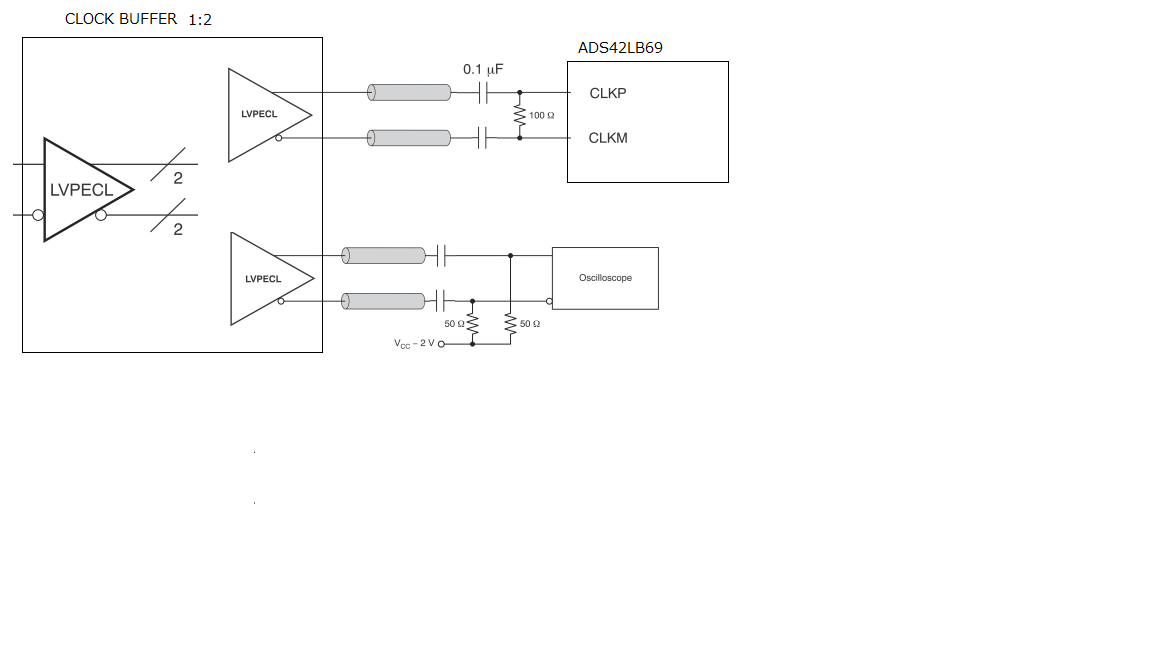

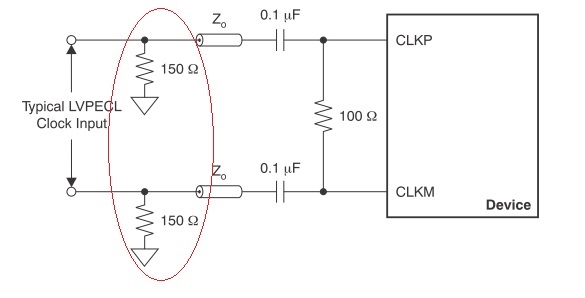

Using circuit as same as Figure 117 of ADS42LB69 datasheet except having 150ohm resistors (CLK source impedance is 50ohm), 250MHz CLK started and measured CLKOUTP/N pastin below. It took 20us, too long to have a stable CLKOUT. No STANDBY mode but just stop/start clock.

During the 20us, 2 pulses were observed and very narrow(2ns width) spike noise were found.

I am attaching e2e link which I questioned and may be related with.

https://e2e.ti.com/support/data_converters/high_speed_data_converters/f/68/t/376025

I would appreciate for your support.

Best regards,

Masa