Hello,

My team want to use AFE5851EVM and TSW1400EVM to implement our system.

We have tried to combine these two evaluation board,

and use the software on the TI website to capture the data. (AFE5851 and HSDC Pro)

And also have solved some problems on it.

Now we want to add some functions into the firmware for FPGA.

So we have to get the verilog source code for the AFE5851EVM.

Because we tried some other ADC boards to capture data before. (AFE5808、5809)

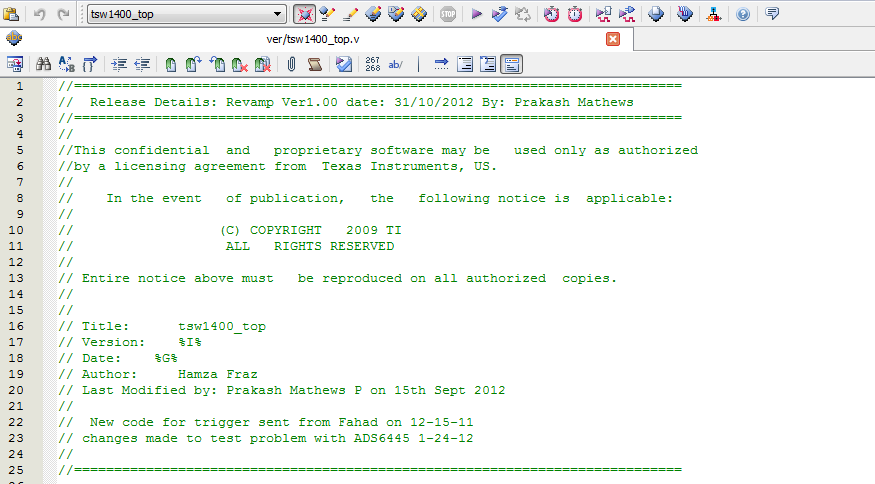

I have got a version of verilog source code.(like below picture)

But it seems not work for AFE5851.

My questions are:

- Does the version verilog source code work for AFE5851EVM?

If it can work for AFE5851EVM, then what settings do I changes?

If it can not work for AFE5851EVM, where can I get the correct version source code?

Kind regards,

Jhin Ci

My email:

JhinCiHong19901008HY@gmail.com