Hi,

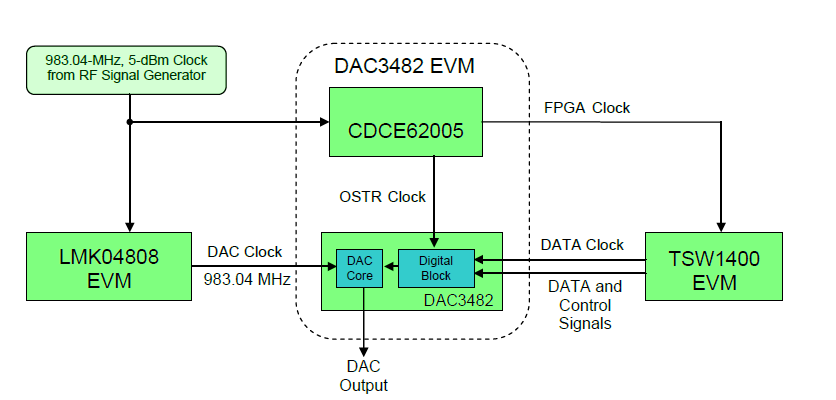

I am trying to setup CW signal of 30MHz using TSW1400 and DAC3482EVM using external DACCLK supplied by LMK04808 EVM but could not get signal out properly, I got FIFO collision alarms. Setup block diagram picture provided below:

DAC3482EVM is modified with the following:

- R154 and R155 is removed

-R124 and R125 jumper is installed

-LMK04808 EVM is programed with 983.04MHz LVPECL 1600mVpp. CLKout0/0* wired to J23 and J22 of DAC3482EVM

-DACCLK=983.04MHz supplied by LMK04808

-FPGACLK=61.44MHz supplied by SigGen CDCE62005 Y3=983.04MHz/16

-OSTR=983.04MHz/64

-Interpolation 4X

-TSW1400EVM data rate set to 245.76MHz

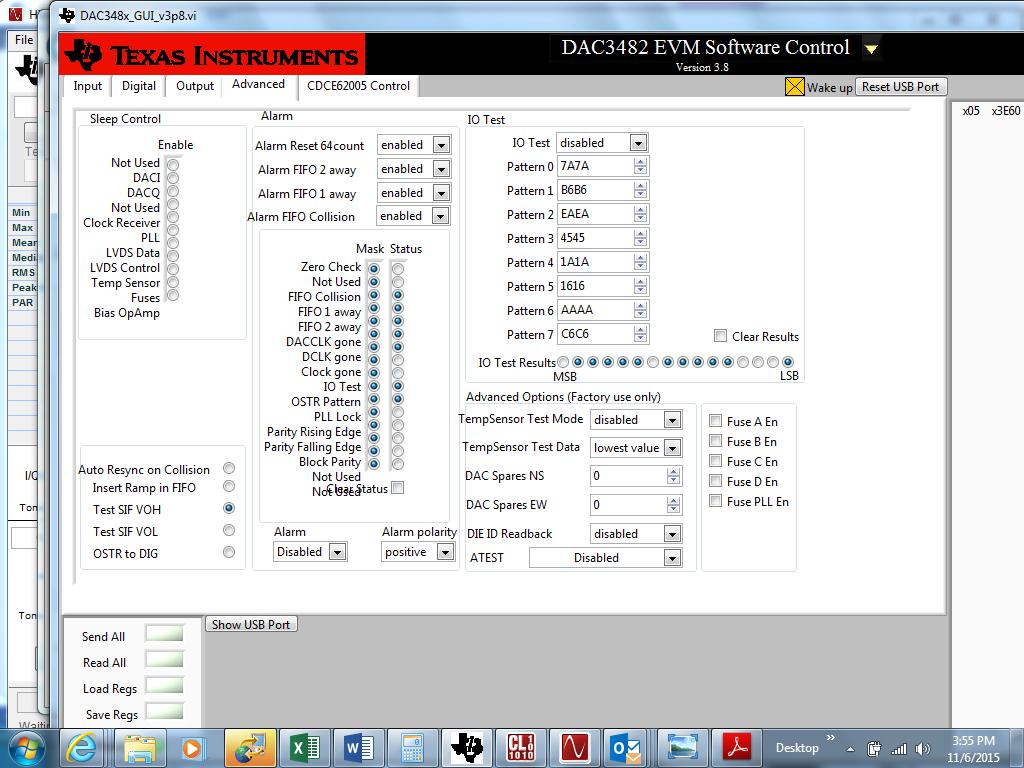

What might be wrong here and how can I correct it? The FIFO Alarm GUI picture shown below

Thanks!