Hi,

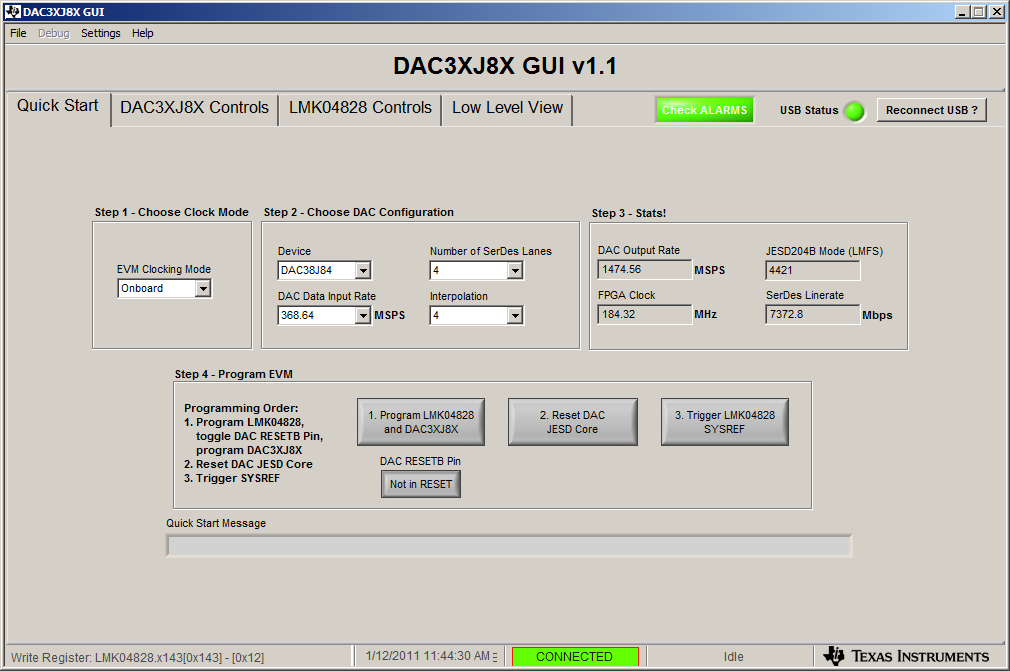

I am trying to establish the JESD link between Dac39J82 and FPGA. I am following the Initialization set up sequence at page 132 of the DAC39J82 specs.

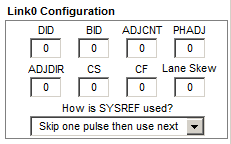

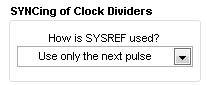

After I feed in a single Sysref pulse, (and I did make sure this pulse happened by monitoring it on the oscilloscope), I did not see the Sync signal come out from the SYNCB pin of the Dac. I have been stuck for a couple of days. Can anybody throw some lights on this?

Thanks a lot.

Hao