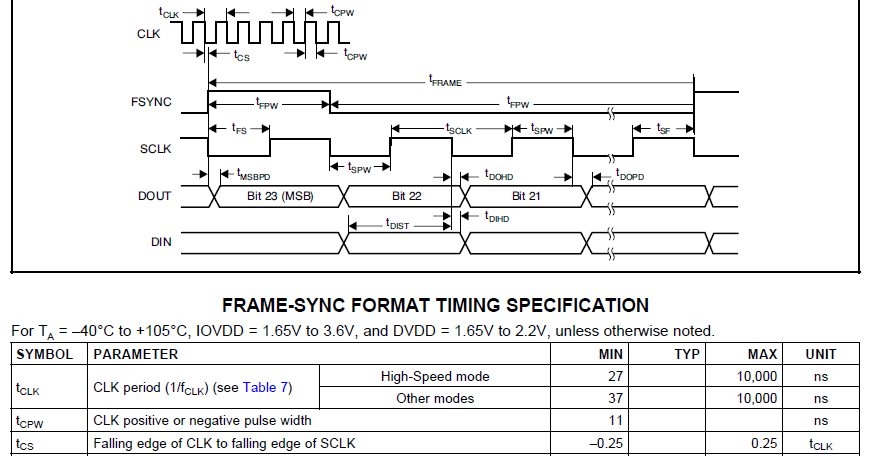

When I read the datasheet about Frame-SYNC FORMAT TIMING. I realize the time of Falling edge of CLK to Falling edge of SCLK (tCS).

They say: tCS is (-0.25,+0.25)tCLK. And SCLK must be continuously running and limited to ratios of 1, 1/2, 1/4, and 1/8 of fCLK.

So I want to know whether I must keep every Falling edge of CLK to Falling edge of SCLK meet the tCK, or I just meet the Timing when the FSYNC goes HIGH.

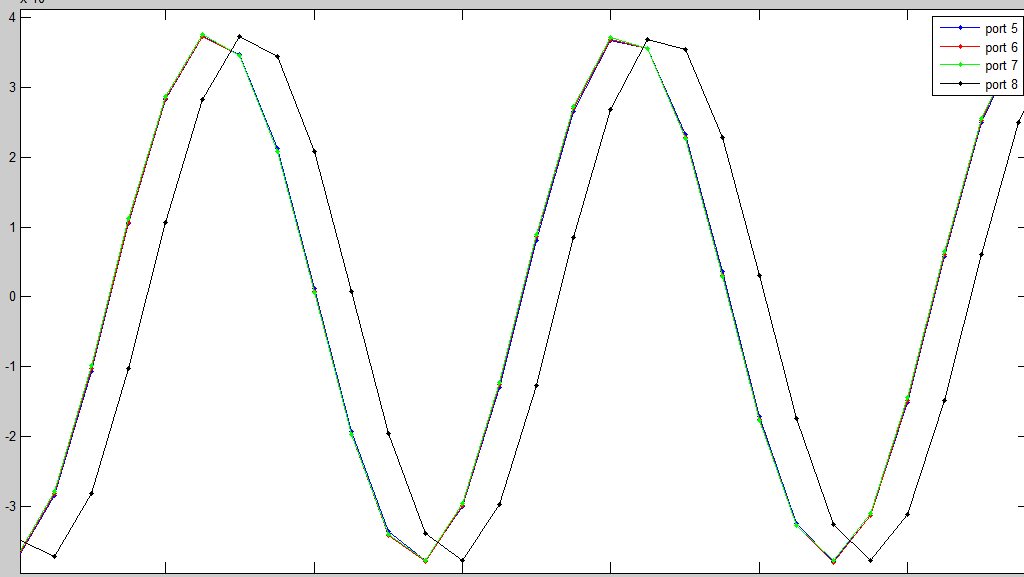

Because my project has some problem. I give the ADS1278 the same sine via OP, but when I see the data from MTALAB, there is something wrong.

Someone told to me that my timing had some problem. I want someone to give me kindly advise about where I should notice when I use the ADS1278.

Thinks for listening.