Hi,

I'm using ADS1299 on my platform. And I cannot read the ID correctly. My steps list below:

(a) Power up my board(BeagleBone Black Board based on AM335X processor)

(b) Initialize and pull-down the START pin, RESET pin, PWDN pin. And delay for a while

(c) Pull up the PWDN pin

(d) Pull up the RESET pin

(e) Delay for at least 1 second

(f) Send command 0x06 to reset

(g) Send command 0x11 to stop continuous reading mode

(h) Send command 0x20 0x00, and then read the ID.

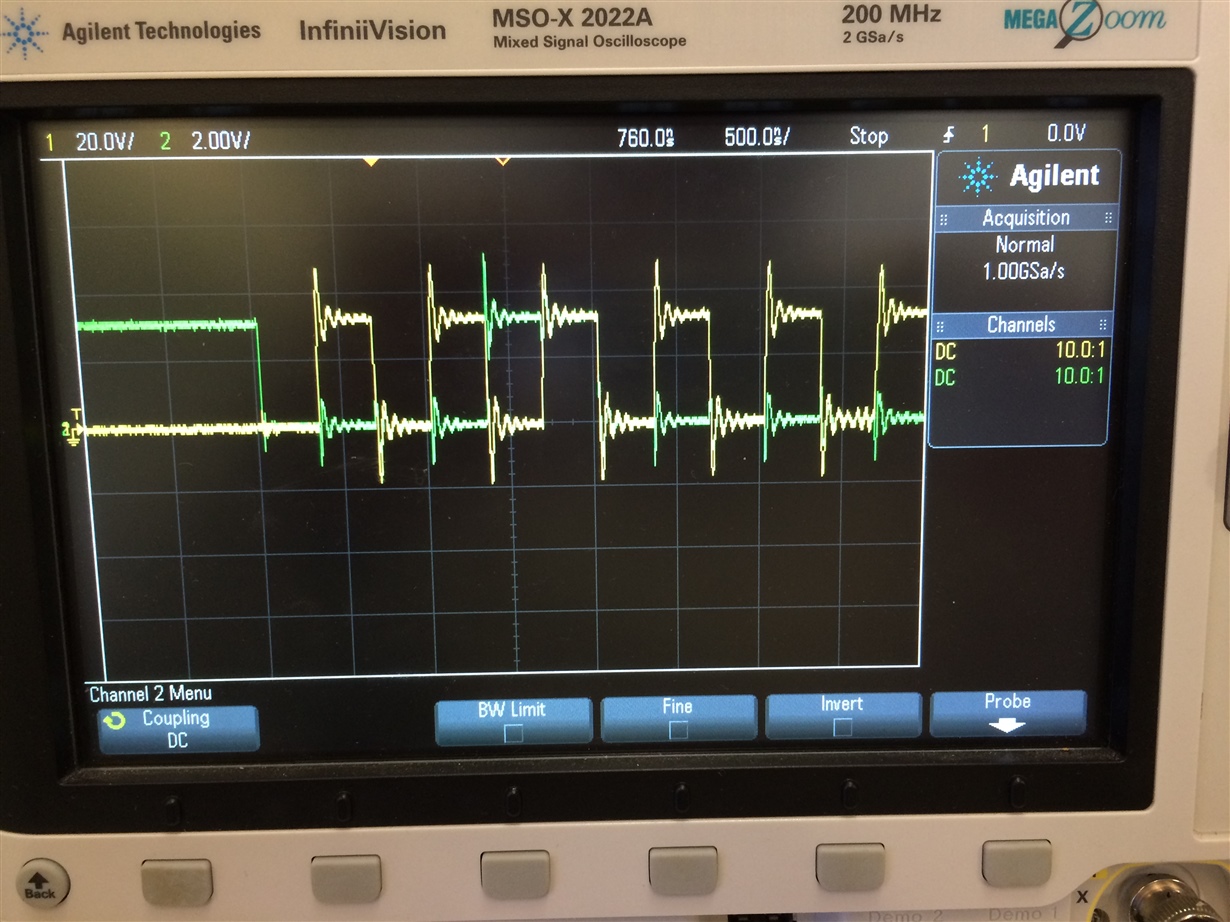

The ID read in my application is incorrect, and each time the data is different, like random. I checked the hardware timing and the data I sent is correct.

Could you please give me some hints about this issue?

Thanks a lot.