Hello

I use the DAC3284 EVM with the DAC348x GUI Version 3.8 on Win7.

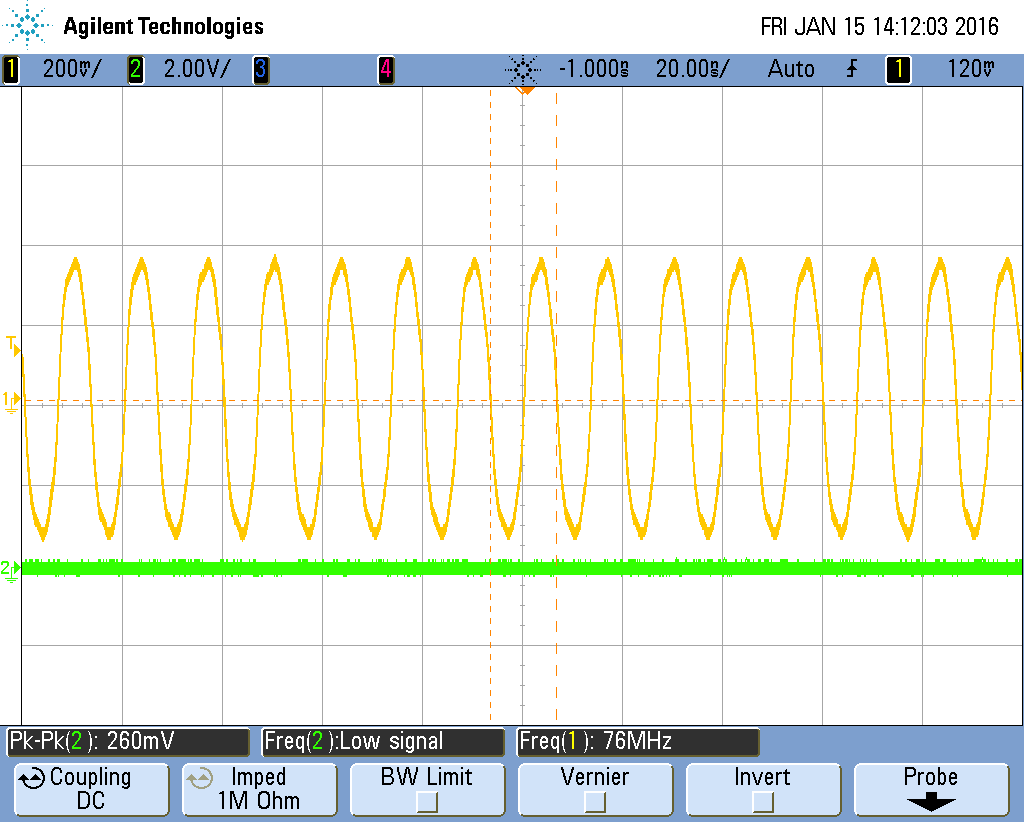

I use the internal clock an have a DACCLK of 75MHz in the test.

I can adjust some parameters of the DAC in the Digital Card, e.g. the Interpolation and the output signal reacts like i expect.

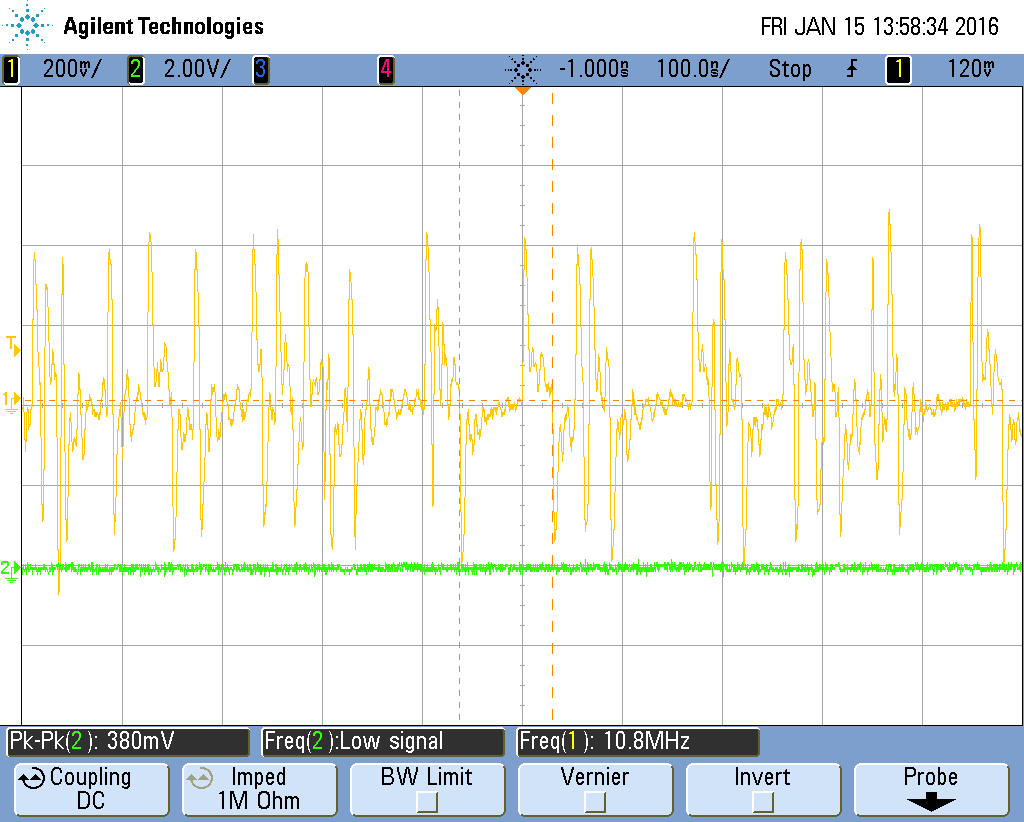

But when I press the "Send All" Button or do changes in the CDCEC62005Control Card, the output is going off, and the internal clock I use is off, too.

The CDCE registers are unchanged since power-up.

Have I wrong adjustments of the CDCE? Or what else could be a reason for that behaviour?

Thanks