Thanks for your fast response !

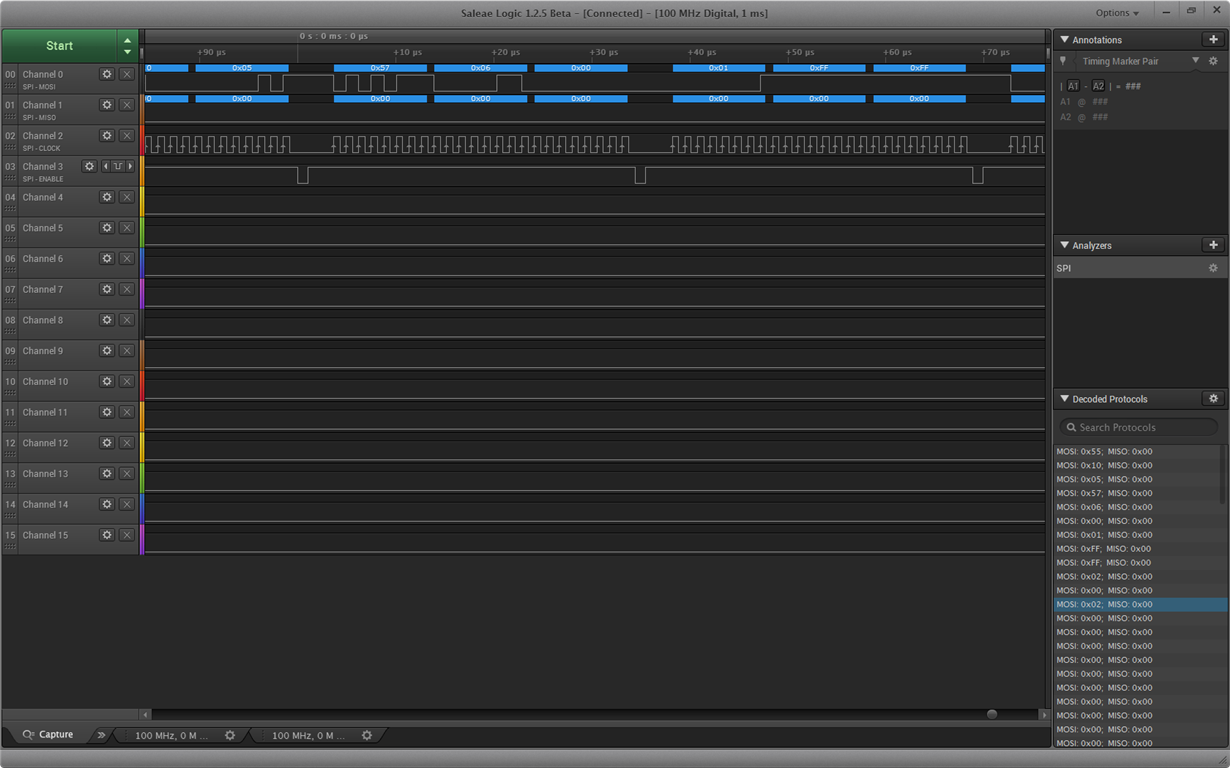

I am not able to attach the Saleae File capture, so sending out a screenshot.

The SPI-CLK is running at 781 KHZ . The following details are regarding the capture-

1> Channel 3 is the Latch signal giving from the DSP(by using a GPIO).

2> I am not able to get latch exactly at LSB of the data.

3> Also as I mentioned before, if I don't give the delay between consecutive transmissions (say between consecutive WRITES) I observe that just the last/recent transmission being transmitted. Might be because I am writing to the register too fast , that it has not completed the previous transmission.

I request for your guidance on these issues.

Thank You,

-Prashanth