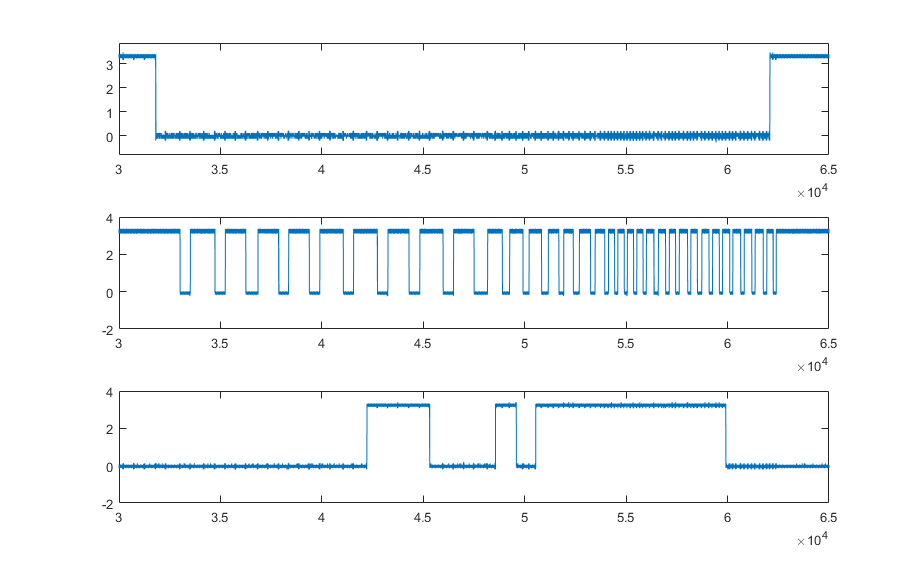

Trying to program the DAC8568 using SPI with no luck. The attached image shows the SYNC_,SCLK, DIN lines (from top to bottom) for an attempt to sequentially program Channel C to full output, note that the entire window shown is about 100ms. For reference, LDAC_ is tied to ground, CLR is high, Vref is 1.65V (with 0.22uF cap to ground) and AVdd is 3.3V (with 1uF cap). The waveforms look clean enough to me, but the DAC8568's output doesn't seem to change from 0, which is the startup condition.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.