Dear TI team,

We are using DAC5686 in one of our design,

We have an input clock frequency of 80 MHz and the data is not interleaved. A 160 MSPS DAC update rate is desired.

For this mode, we can use DIV = 2x assuming the VCO and LPF are optimized around 320 MHz and SEL is set to 2x.

We have generated 10MHz as message frequency with 80MHz Data clock as sampling frequency.

For this we have used following register setting

x"0F00",--dacb_offset_gain_msb

x"0E00",--dacb_gain_lsb

x"0D00",--dacb_offset_lsb

x"0C00",--daca_offset_gain_msb

x"0B00",--daca_gain_lsb

x"0A00",--daca_offset_lsb

x"0900",--config_usb[see PLLVDD]

x"0710",--config_lsb[mode-dualdac,div-1x,sel-x2,counter-disable,full_bypass-disabled]

x"0600",--phase_msb[15:8]

x"0500",--phase_lsb[7:0]

x"0400",--freq_msb[31:24]

x"0300",--freq_umidsb[23:16]

x"0200",--freq_lmidsb[15:8]

x"0100",--freq_lsb[7:0]

x"0000",--chip_ver

x"0803"--config_msb[sif4, 2'complement]

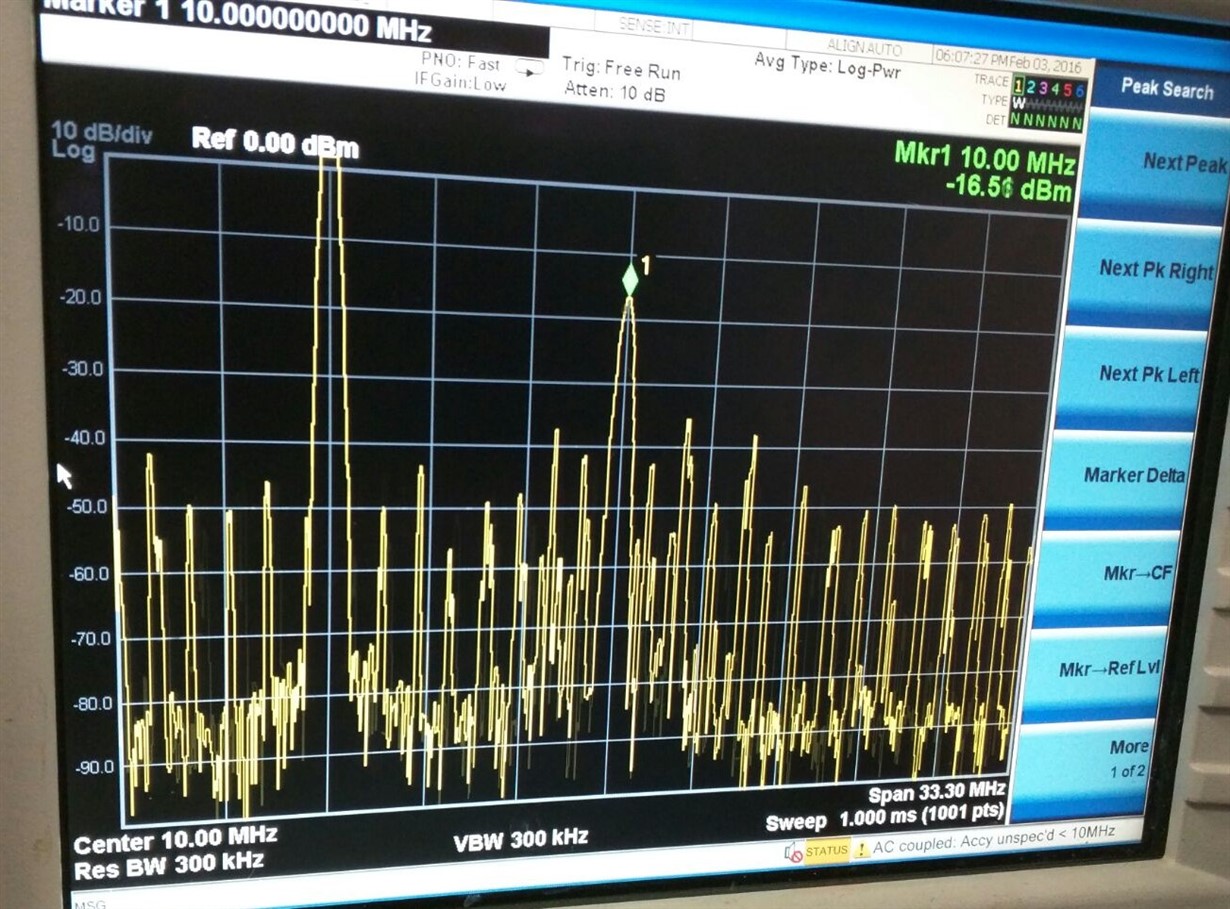

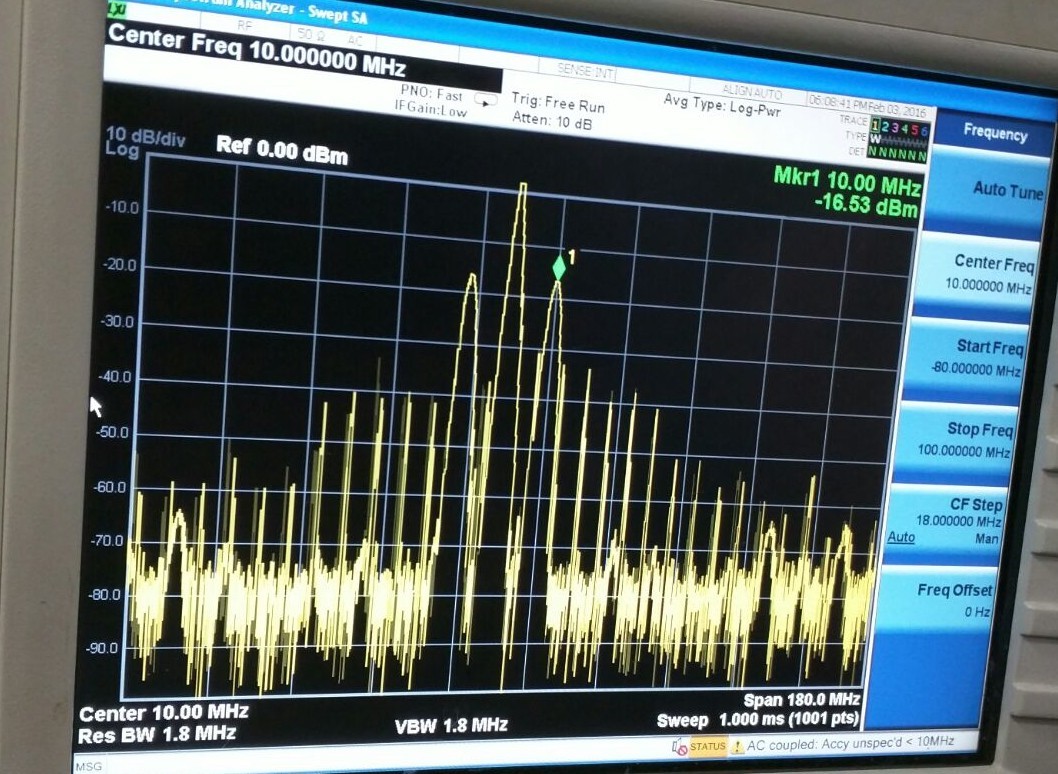

But the output is not clean and Output level is very low <10 mV. We have also monitored PLLLOCK which is locked.

Is any thing I need to change in the register setting. please suggest me any other changes required to get clean output.

regards,

syed