Hi,

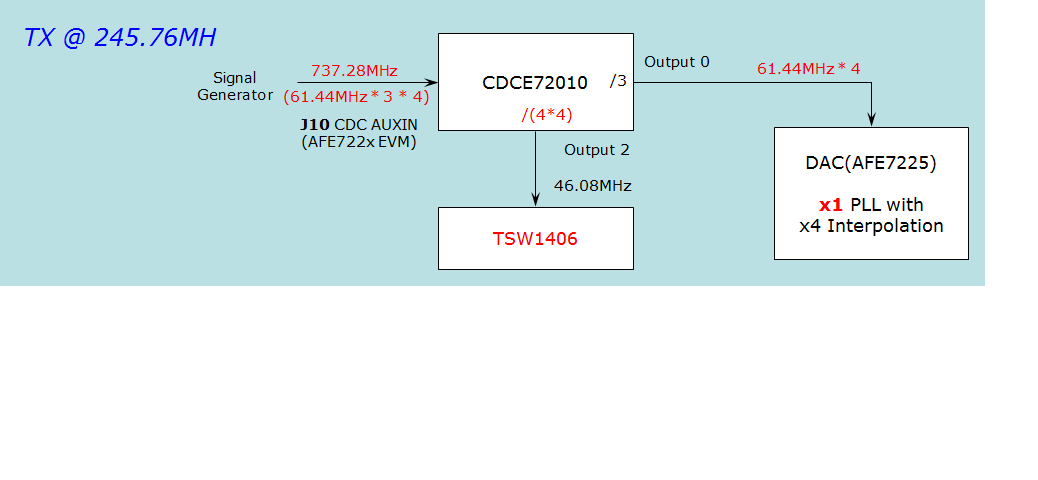

I have a afe7225 EVM and TSW1406 and want to test the DAC performance. the CDC AUX input is 368.64MHz, output 0 divider is 3, output 2 divider is 8. divideDAC clock is 1, interpolation is 4. test file is :WCDMA_TM1_complexIF30MHz_Fdata122.88MHz-1000.TSW. I got the signal on the spectrum analyzer at 7MHz and the bandwidth is 2MHz, and there is a lot of suprious on the spectrum. what's wrong with my configuration or test file?

thank

David