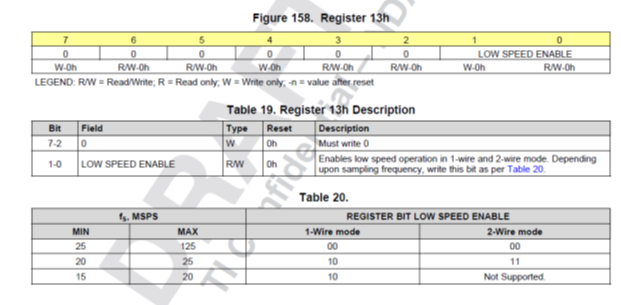

We're using an ADC3243 to sample at several low frequencies. Operation is correct at the following frequencies: 60.0 MHz, 30.975 MHz, 25 MHz, and 20.265 MHz. However, when attempting to operate at 12.159 MHz, the output FCLK is no longer a square wave. It is still periodic, but it not the correct frequency and has short, positive pulses where it should be low. DCLK does not look correct either.

Below is a register dump when this condition occurs. The input clock is good quality and the correct frequency, and all other frequencies listed above work correctly. The datasheet indicates that sampling is supported down to 10 MSPS. Any idea what needs to be changed or if sampling down to 10 MSPS is actually supported?

Register Addr Value

============= =======

0x01 0x00

0x03 0x00

0x04 0x01

0x05 0x00

0x06 0x00

0x07 0x00

0x09 0x03

0x0A 0x00

0x0B 0x00

0x0E 0xAA

0x0F 0x00

0x15 0x00

0x25 0x00

0x27 0x00

0x41D 0x00

0x422 0x02

0x434 0x00

0x439 0x00

0x51D 0x00

0x522 0x02

0x534 0x00

0x539 0x00

0x608 0x00

0x70A 0x01