I use the ADC12J4000EVM connected with the ZC706 Zync board from Xilinx via TSW14J10 board.

those link indicate that boards are compatible

http://www.xilinx.com/products/technology/high-speed-serial/jesd2014-reference-designs.html

http://www.ti.com/tool/tsw14j10evm

however, sync signal and sysref signal are connected to bank 11 off the FPGA and this bank is supply with 2.5V.

sync signal come from FPGA to ADC12J4000 (G12, G13 FMC pins and AF19, AG19 FPGA pins)

sysref signal come from LMK04828 to FPGA (G9, G10 FMC pins and AH19, AJ19 FPGA pins)

sysref signal is AC coupled and regards to AR 40191 from Xilinx the compatibility seems to be ok.

for sync signal the absolute Maximum rating is V(va19)+0.15= 2.05V on the input of ADC12J4000. So the component can be damage by 2.5V level.

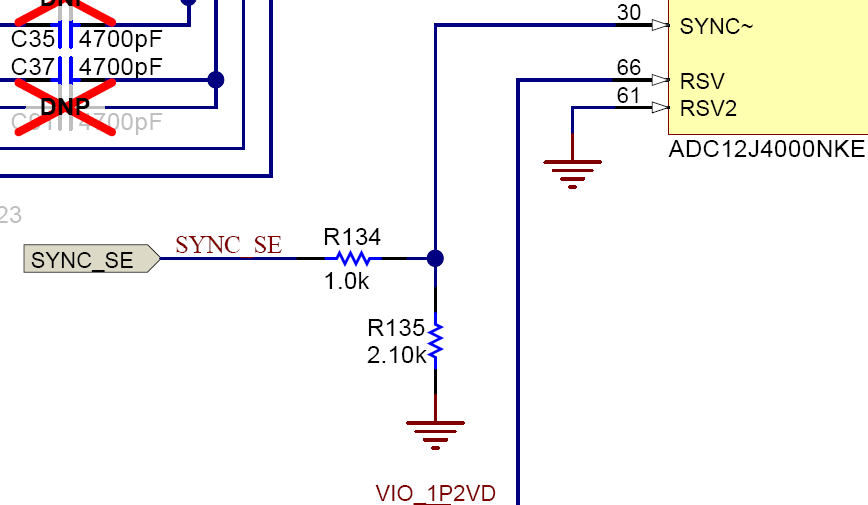

the alternate sync_se signal is also on a 2.5V powered pin.

Do you have a solution to this issue?

regards,

Arnaud