Hi

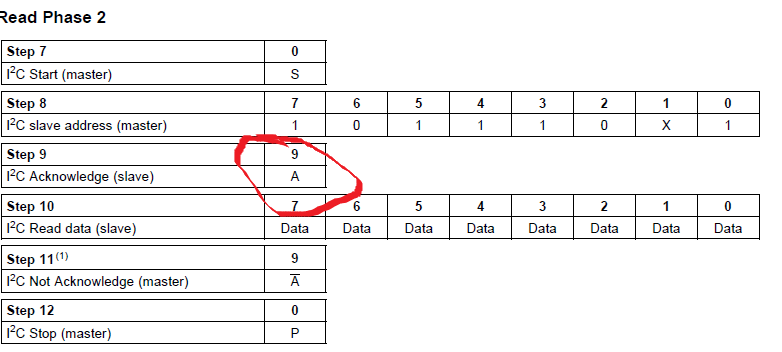

From the spec, I found that TVP5150 needs some delay before the master sending stop condition.

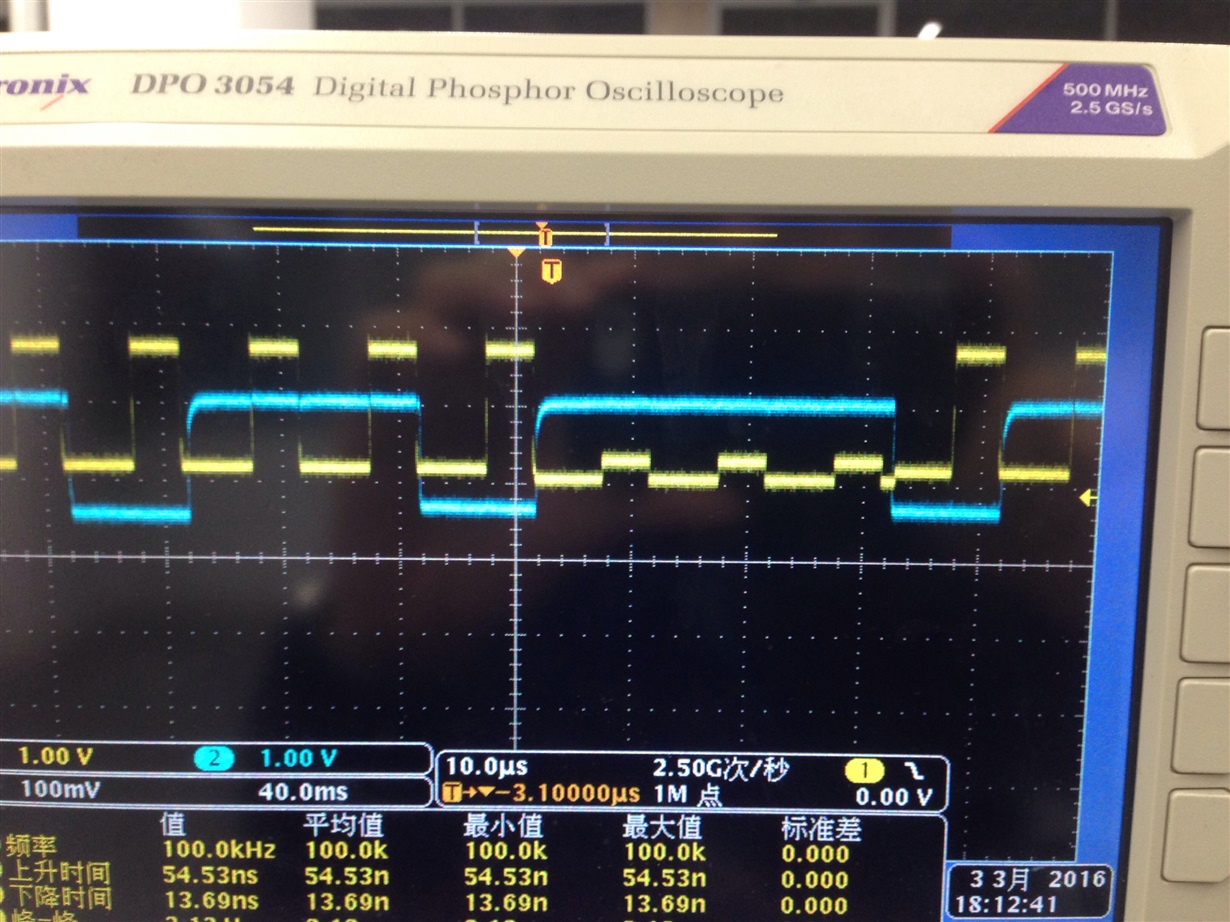

While I measured that TVP5150 pulled the SCL line low after it sending ACK, that caused the master would read wrong data.

Please help us to check it .Thanks