Hi all,

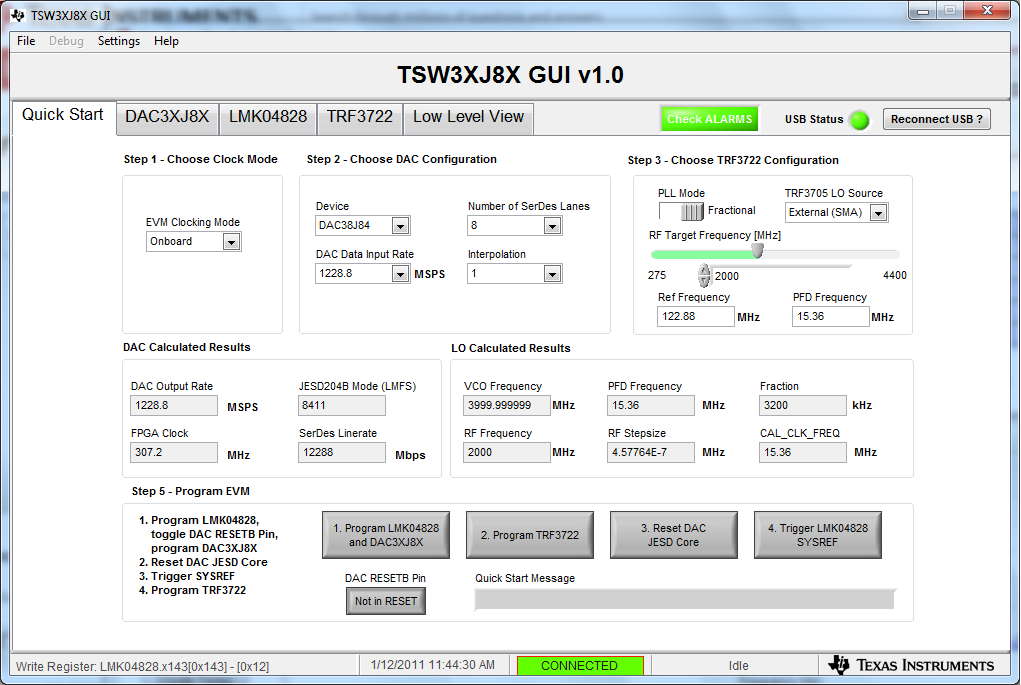

I am using the TI Tx board TSW38J84EVM together with the TSW14J56EVM pattern generator board.

I am using the DAC3XJ84_LMF_841 image file for the TSW14J56 , and the DAC is also configured to work with 8 lanes.

Everything is working fine, excluding when the maximum input sampling rate (Fs) is equal to 1228.8 MSps.

In this situation the output spectrum only makes sense if I use a number of samples <= 1024.

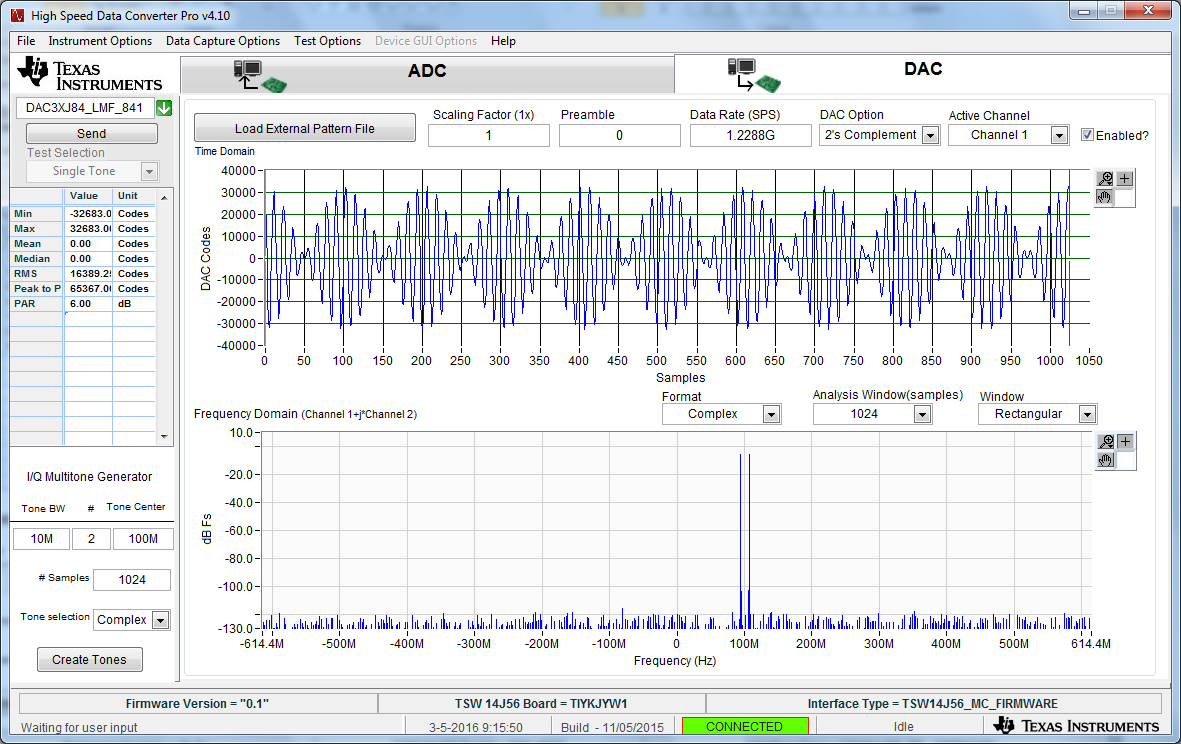

For instance, if I use the TSW14J56EVM I/Q tone generator, to generate the following signal:

- Tone BW = 10M

- #Tones = 2

- Tones Center = 100M

- Tones selection = complex

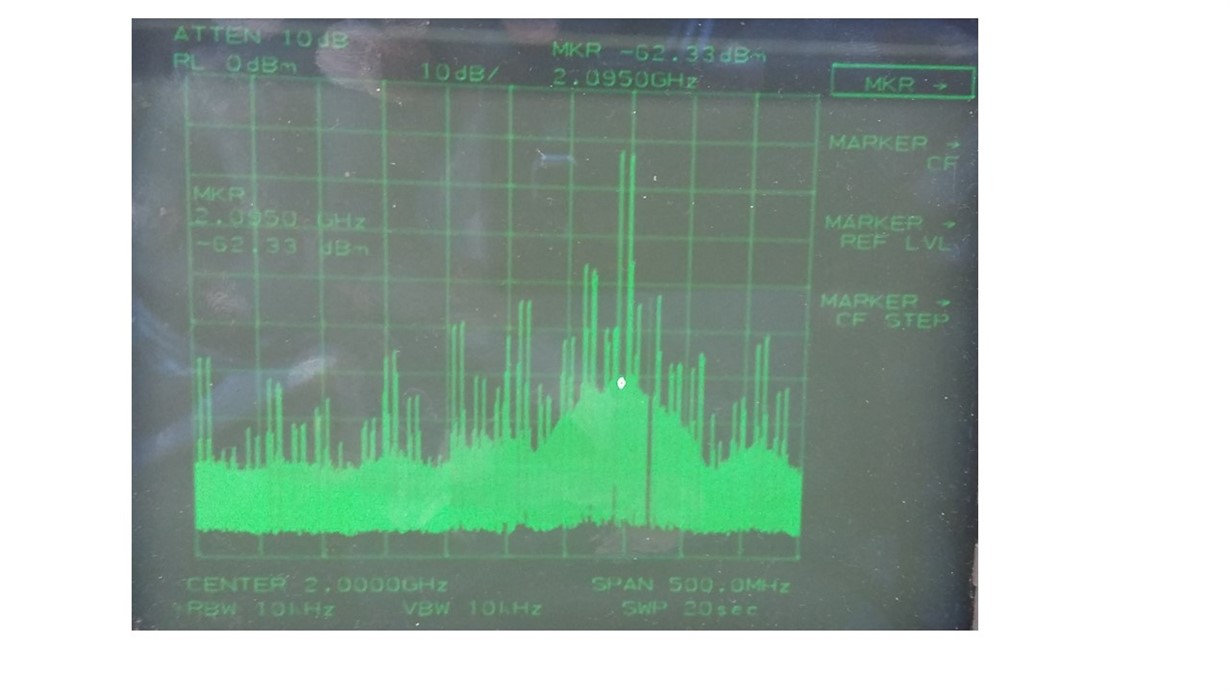

The output signal seen in the spectrum analyzer it is fine and according to what I was expecting.

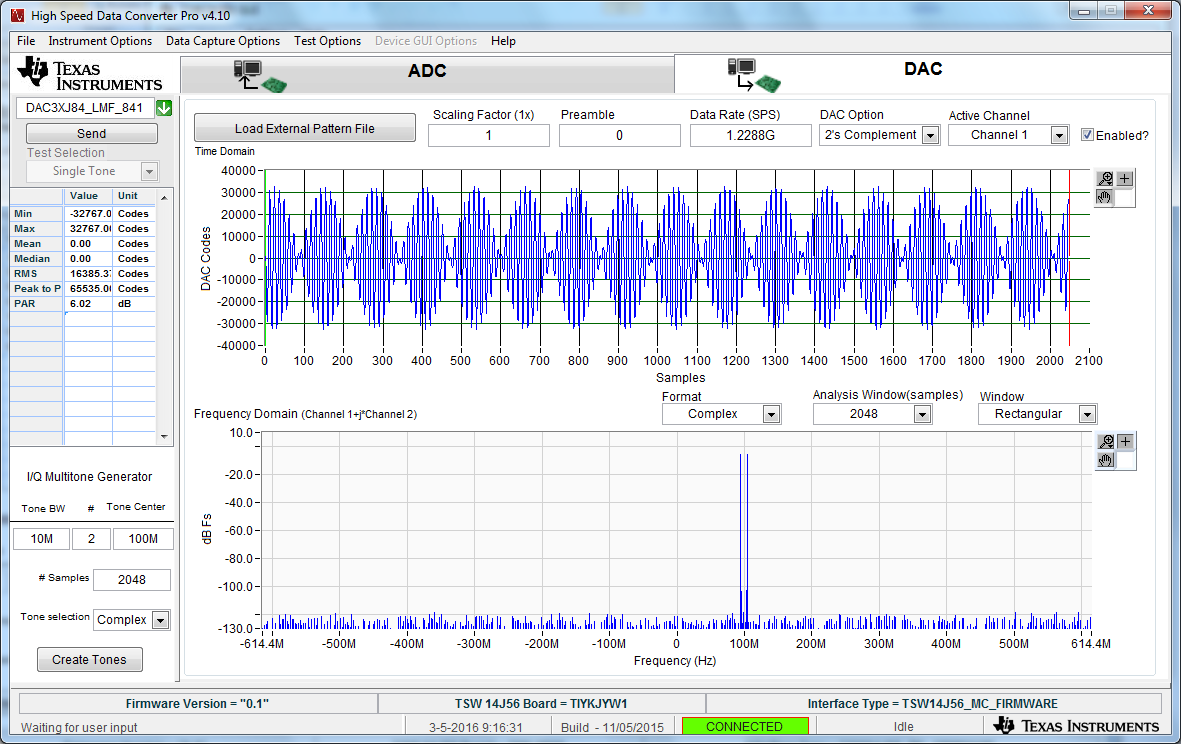

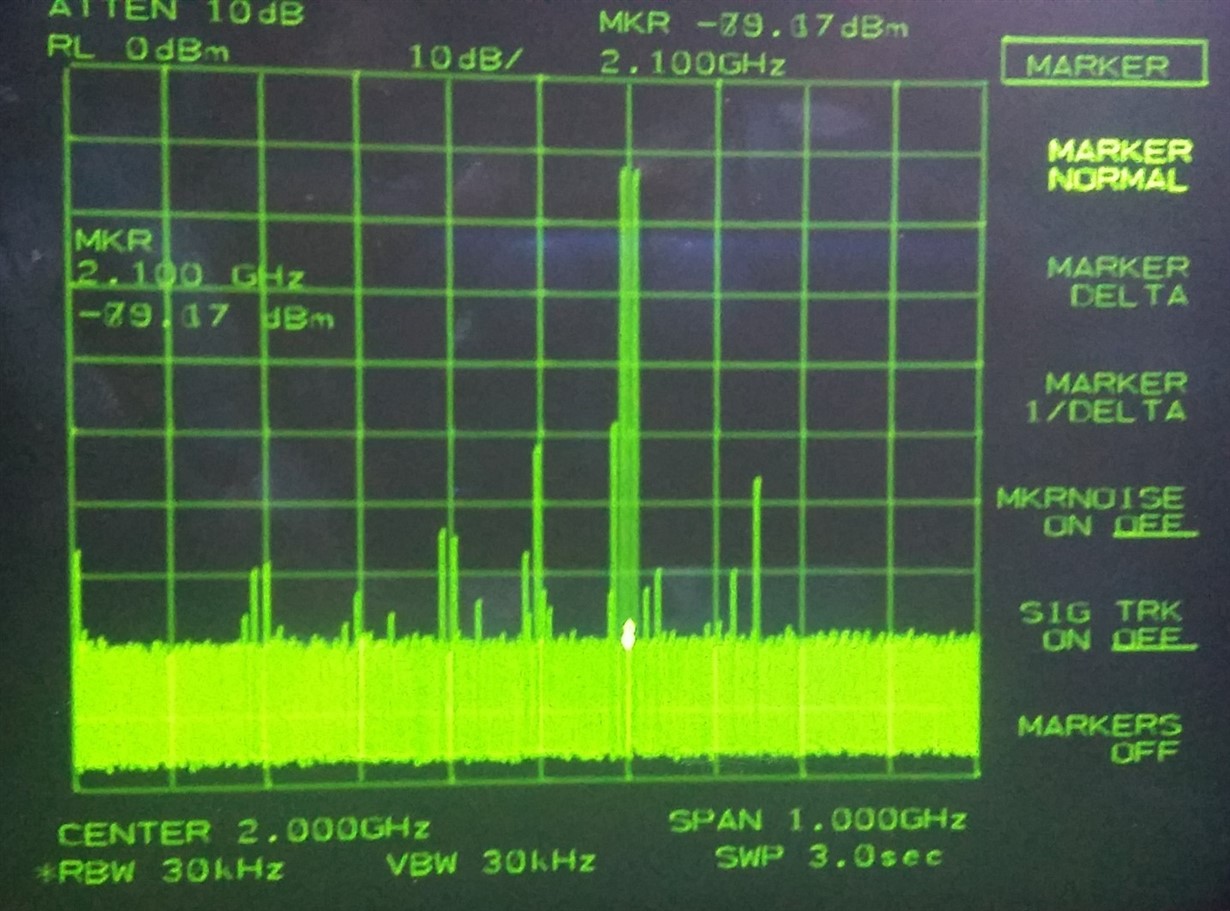

Then, if I change just the number of samples to 2048, the output spectrum does not makes sense, giving the idea that there is a problem in the samples that the DAC is reading...

As far as I understand, this is only happening in the maximum sampling rate case. Have you faced this problem while using the maximum sampling rate?

Thank you.

Regards,

Andre