Dears.

Can I get config file for this operating case?

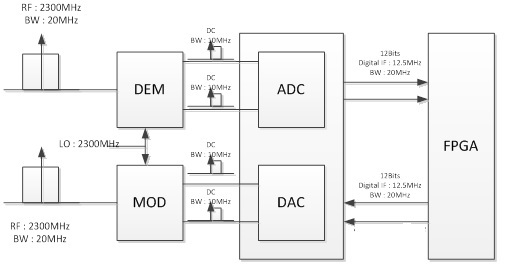

- AFE7225 operating CLK is 61.44MHz

- RF 2300MHz is changed DC I and Q through demodulator

- Through demodulator in internal ADC, the signal is changed Digital IF 12.5MHz BW : 20MHz

- ADC OUT CLK 50MHz and 12Bits Digital IF 12.5MHz, BW 20MHz signal transmit 1 time per a CLK

- FPGA read the data to work to ADC OUT CLK

- FPGA transmit DAC IN CLK and 12Bits Digital IF 12.5MHz, BW 20MHz signal 1 time per a CLK

- DAC make to change analog DC I and Q through modulator

- DC I and Q signal in modulator make RF signal

It is difficult to test with AFE7225EVM

The CDCE72010 does not output0, output4 from the AFE7225EVM.

When the CLK input J10 port, CLK is reversed in signal generator.