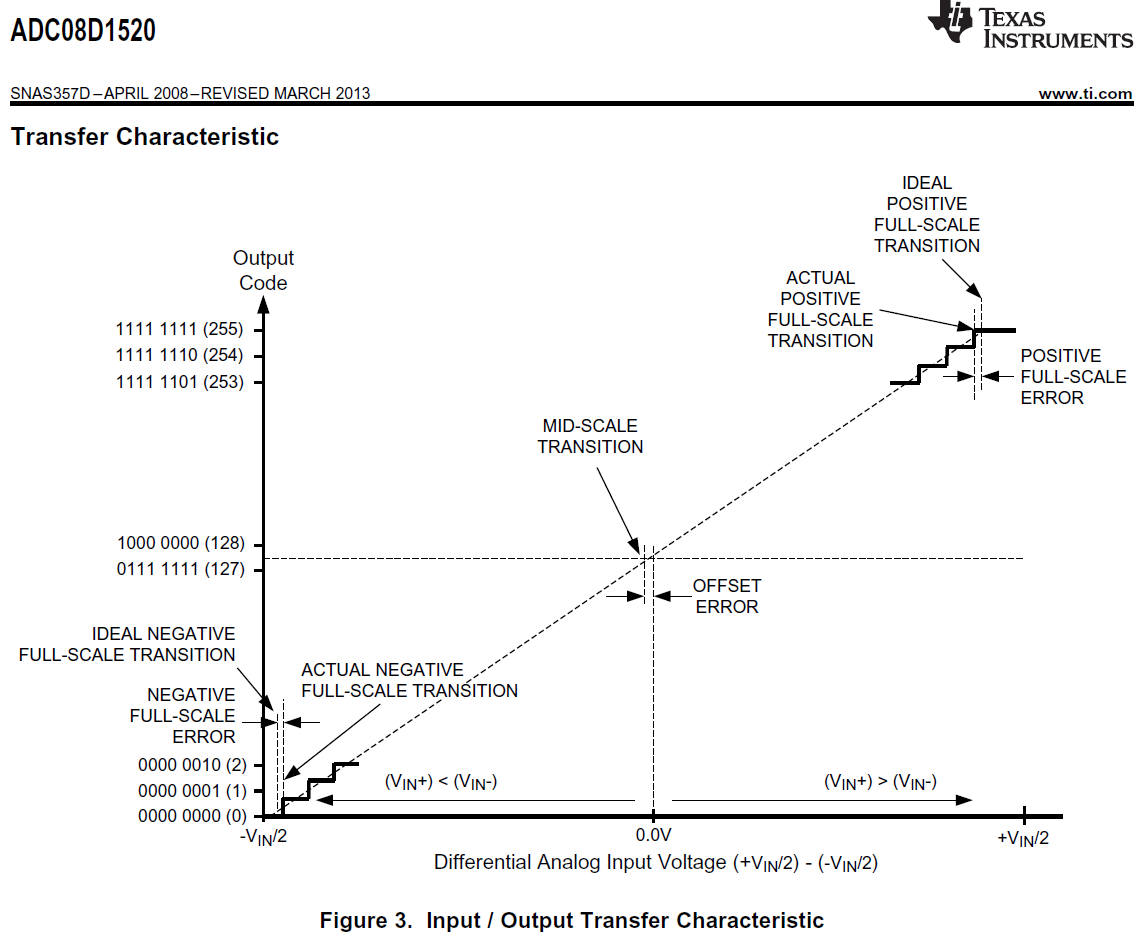

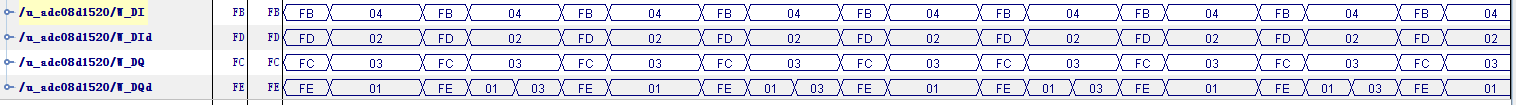

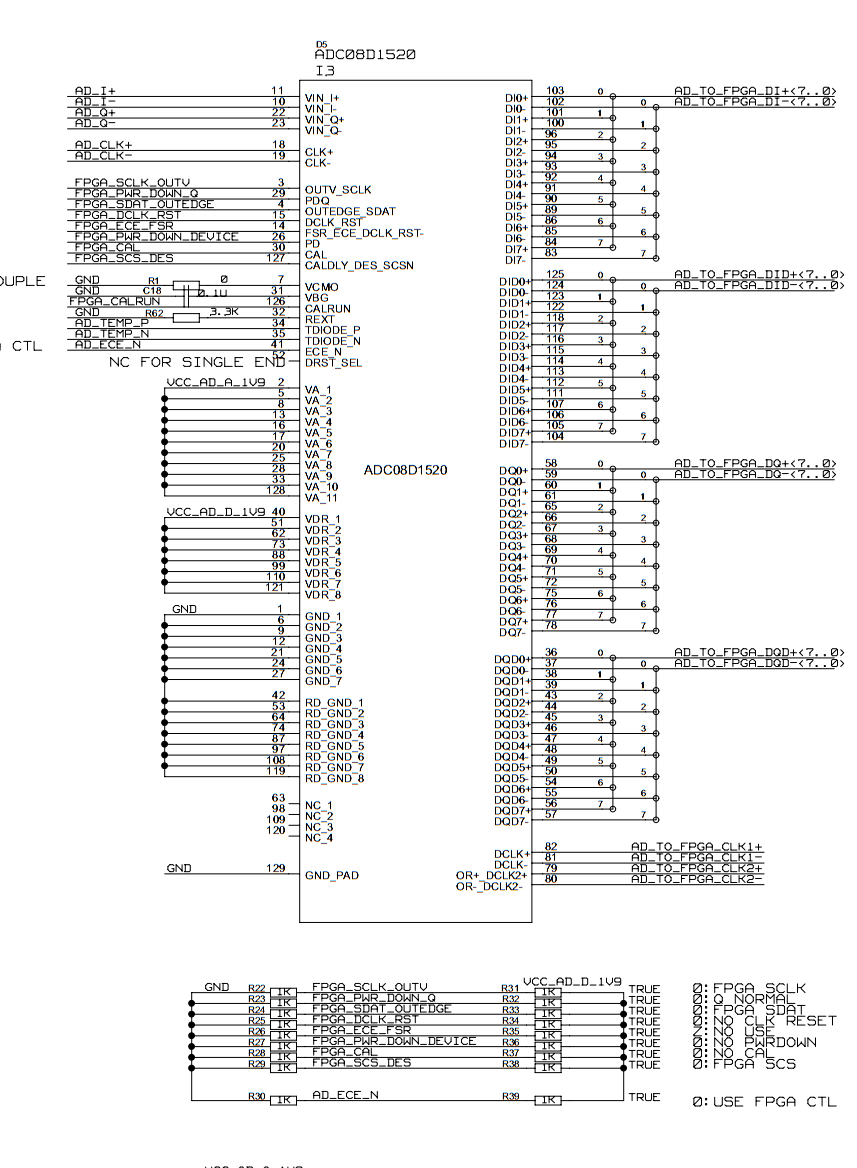

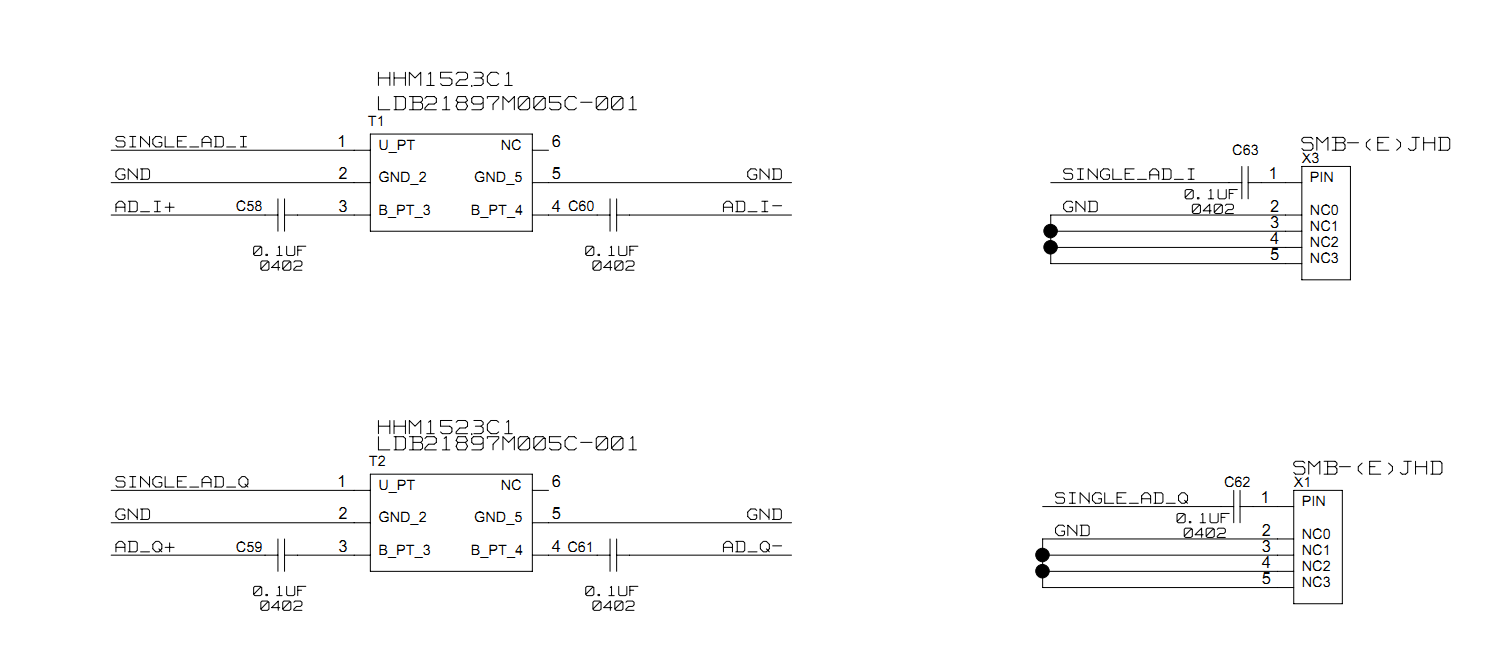

hello ,i try to use FPGA to configure this adc,according to the adc25d1520.v that provided from the forum , i send thte 8 register value through sclk,sdat,scs pin in extended control mde,(pin 41 is low),and set all the other like fsr pin high z. But the sample result is no right according to the FPGA sample data,the sampled data is always 8'h7f or 8'h80/81 when i did not connect any signal to the I/Q input .

is there anything worong with my configuration? the sample clock is 250Mhz provided by lmx2541 pll,all the 8 regiser value is given as the default value described in the datasheeet.

if it wrong ,what is the right configuration step? i only need to confirm that the adc funtion is right.

thank you.