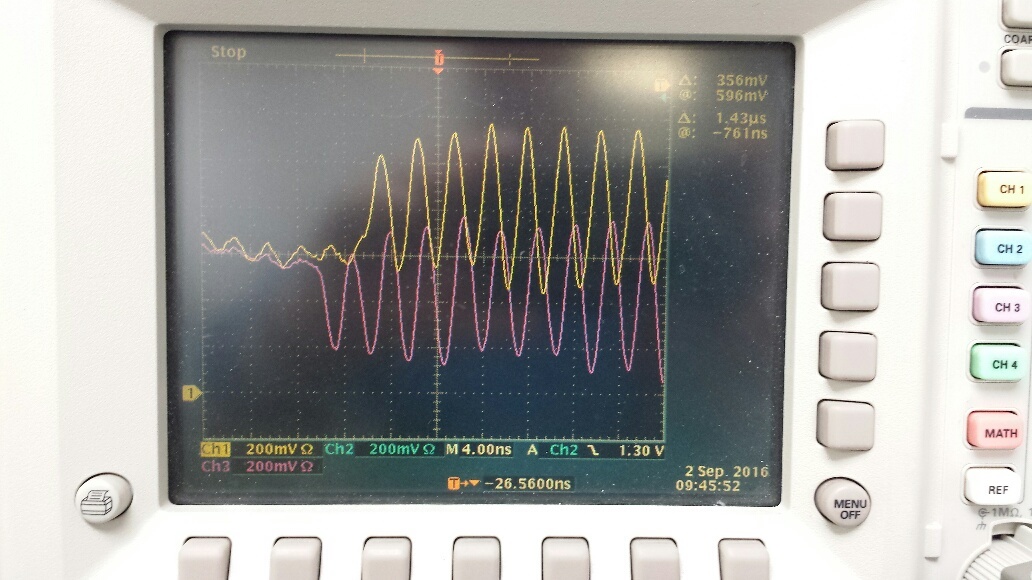

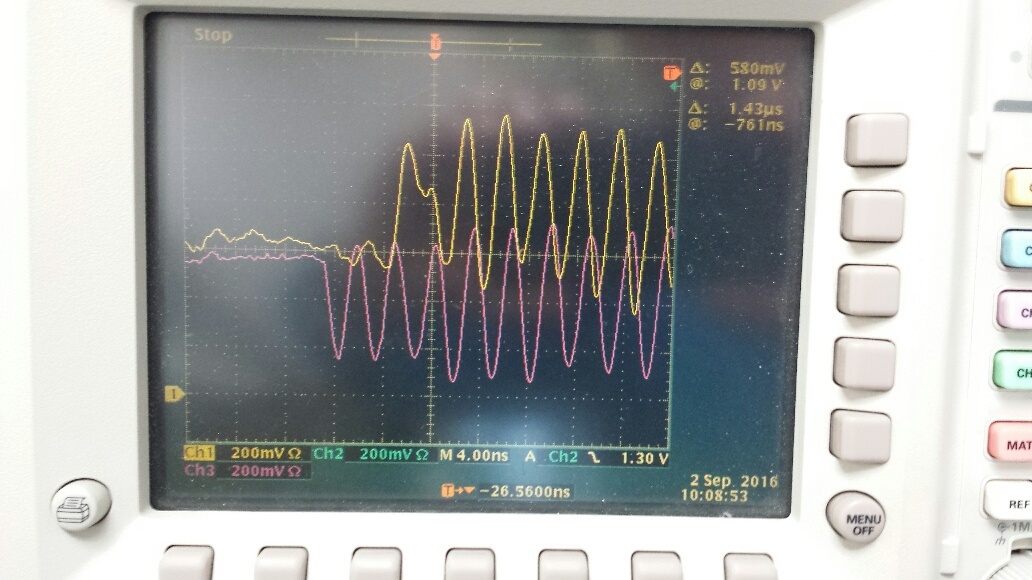

I'm using the DCLK_RST functionality of the ADC12D1600. I begin by writing bit 0 of address 0xE to0 to enable this functionality. I then generate a synchronous dummy reset pulse (high for 3000 sample clock periods) on DCLK_RST. Finally, I generate another reset pulse on DCLK_RST. I have noticed that while this second reset pulse is asserted, the ADC DCLK output will stop either low or high. Is this expected? I thought the DCLK was supposed to come out of this second reset in a known way.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.