Hello Experts,

We are trying to communicate with TI's ADS131A04 using SPI in Asynchronous Interrupt Mode. Our MCU is STM32L486 from ST. After powering up ADC and pulling CS low, we begin reading from ADC according to the "10.4 Initialization Set Up" ADS131A04 SBAS590A documentation.

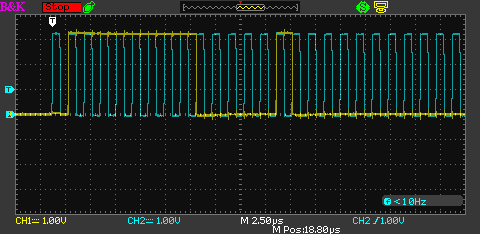

We are expecting to receive the 0xFF04 as the ADC READY signal. However, we are receiving the 0x7F82, which is 0xFF04 shifted 1 bit down the SPI stream. Please see attached screenshot ADS131A04-READY.png. From this image, you can see that DOUT is set by ADC at the second SCLK pulse.

By looking on the Figure 57 on page 41 it seems that ADC should have DOUT settled at the very first falling SCLK edge.

Question: is DOUT suppose to be read at the very first falling edge of SCLK, or we have to issue a dummy SCLK pulses at some moments? If so, when should we issue such dummy SCLK pulses?

Other details: we are using CPOL=0, CPHA=1, have enough delay after CS is pulled down, signals are clear and do not have noise, the results are consistent for various clock rates.