We are interfacing an ADS1278EVM to the lcdkc6748 using SPI1 port. We are working with the MM0 as power source for the ads1278evm through the header J5 and are also using the Starterware platform wtih SPI protocol. Our clock signal (4MHz) wich is the same sclock signal comes from a signal generator, the sampling frequency is aprox 15KHz in low power mode and we are also using a GPIO port to sensing the DRDY signal and this starts communication. DSP is in slave mode that it is because (CLCK and SCLK are always running).

We have understood from datasheet that SCLK and DRDY signals are synchronized each other but when we see these signals in the oscilloscope we realized they don't, which is why sometimes we received streams shifted one bit to the left or right.

Which could be our problem? Maybe any kind of hysteresis?

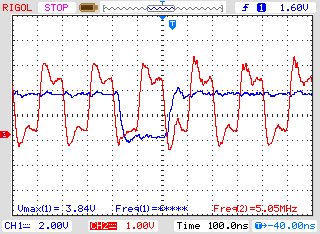

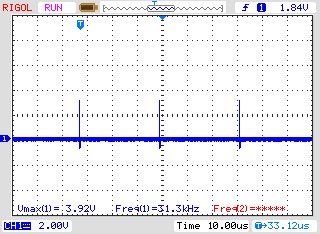

The resulting signals are as follows:

Fig1 and 2 DRDY Signal (blue) Vs SCLK (red)