Hi,

One of customers is using the ADS1282 in his design and needs to convert the input data at 2ksps. The inputs need to be selected alternatively; i.e. Ch1 alternated with Ch2. The data rate needs to maintained at 2Ksps.

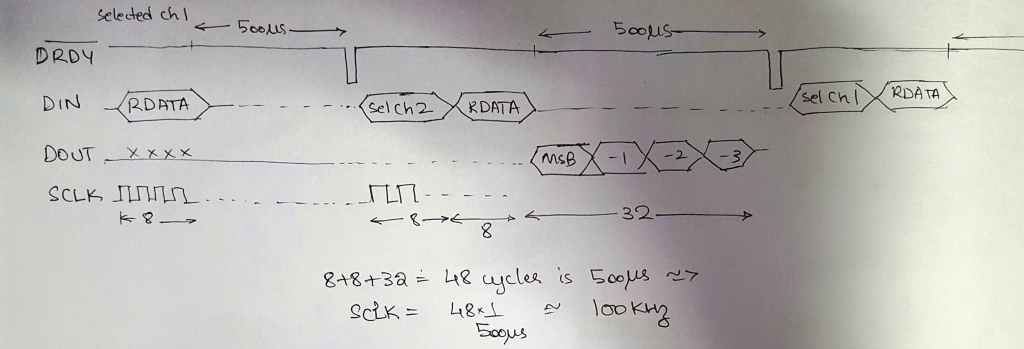

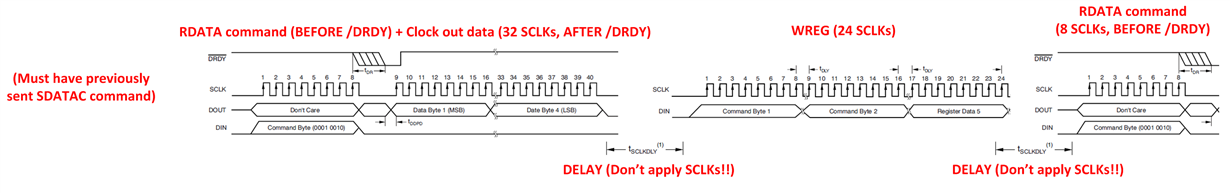

I plan to use "Read data by command" as we need to change the input channel alternatively. I have attached the timing diagram for this application below.

I am trying to change the input Mux setting and issue RDATA before reading the data on DOUT in order to reduce the sample to sample delay. Is this sequence possible? Is it also possible to read out DOUT at the same time write to the device on DIN as DIN and DOUT are separate pins from the DSP? This will ensure that the read and config operation happens in parallel. The above scheme assumes that the "tdr" time is 1/Fdata rate which is given as the maximum value. What would be the minimum time after issuing RDATA and the DRDY going low?

If the above scheme is not possible (RDATA command before reading data), can we read the data first and then issue the RDATA command?

Is there a better solution for this?