Other Parts Discussed in Thread: ADC12J4000EVM, ADC12J4000, LMK04828

Hi everyone,

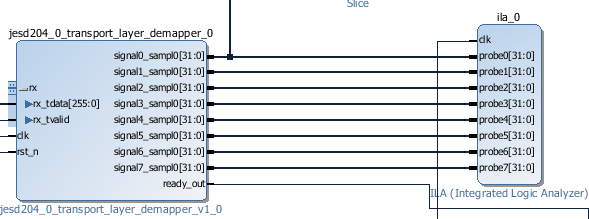

I built a FPGA project for ADC12J4000EVM.

I configured the board through ADC12J4000EVM GUI.

On the ADC side, the configurations are as follows.

On-board Fs=3760Msps.

Bypass Mode; DDR

L = 8

K = 10

Scrambler off

On the FPGA side, the JESD configurations are as follows.

Refclk = 188MHz

Coreclk = 94MHz

L = 8

M = 10

F = 2

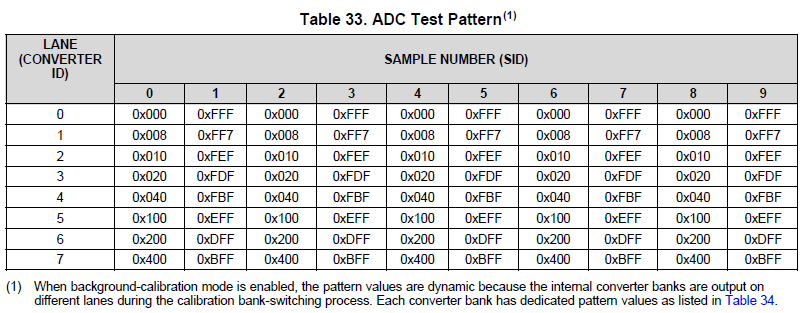

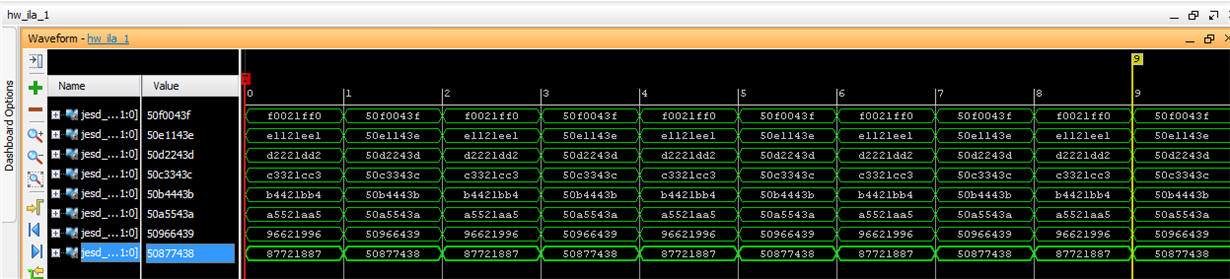

According to page 48 of ADC12J4000 datasheet, the ADC test pattern should be as follows.

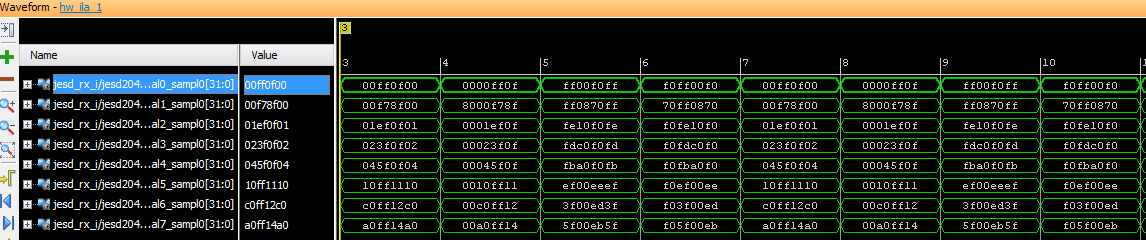

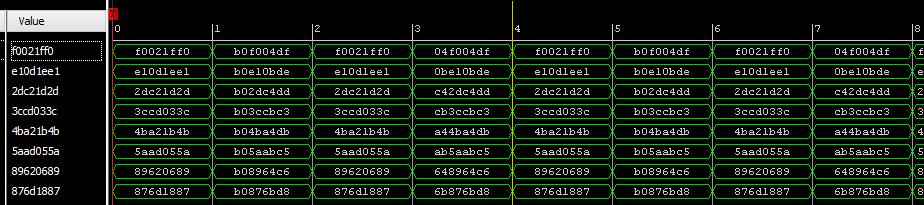

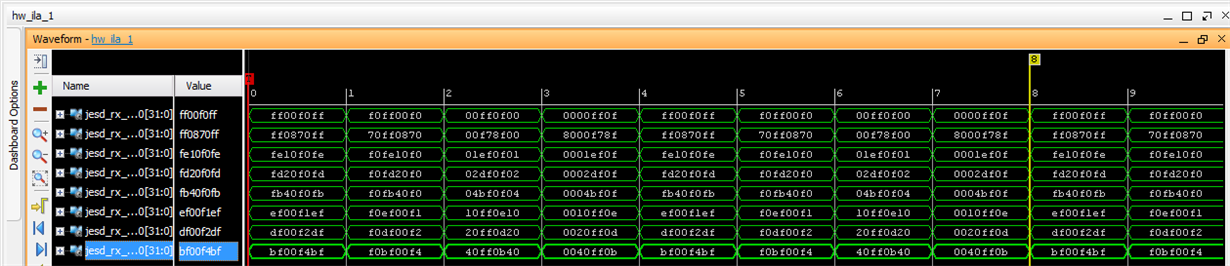

I tried the Test Pattern mode, and exported the data of 8 lanes through ILA. As follows.

The data from lane 0~2 are the same as the sampled data, while the data from lane 3~7 are not.

Can anyone tell me what I was doing wrong?

Thank you.

Regards,

Tong