Hi Team,

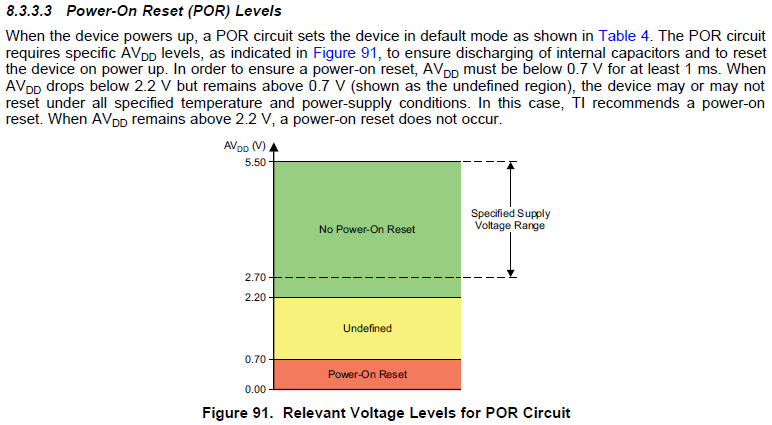

I understood AVDD must be below 0.7V for at least 1ms, and then be increased up to 2.7V(min) to ensure POR.

Could you tell me a state of output voltages of DACs under the condition of AVDD=0~0.7V for DAC7562-Q1?

Does these also show zero volts ?

Best Regards,

Yaita / Japan disty

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.