Hi everybody,

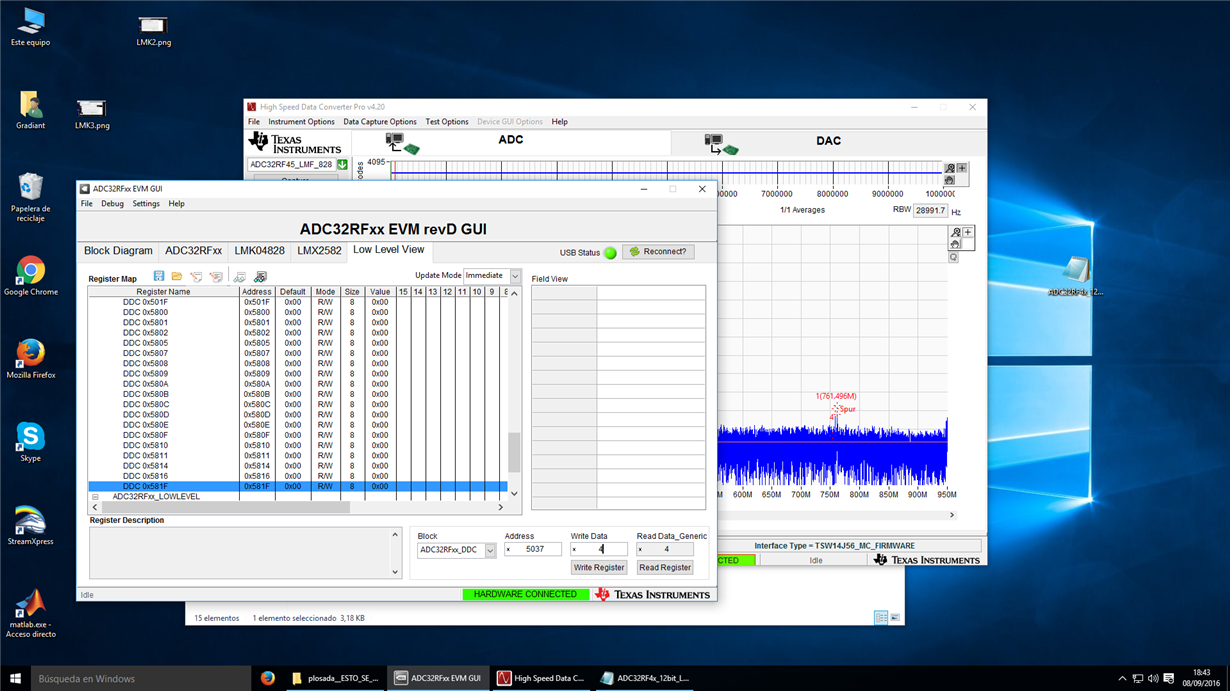

I have been evaluating the ADC32RF45 for a few days by means of an ADC32RF45EVM + TSW14J56EVM and the original cfg files provided along with the EVM's software.Currently I am configuring the EVM so that I can generate the ADC's sampling clock from an external signal generator, and after many tests, I observed that the ADC's performance in terms of interleaving spurs suppression appears to depend on the selected sampling frequency. For example, the spectrum that I get after digitizing a 666 MHz analog tone is:

1500 MSPS: Not very bad

1600 MSPS: Similar thing

1700 MSPS: Interleaving spurs increase quite dramatically and noise floor appears colored (¿?)

1800 MSPS: Same thing but even worse

1900 MSPS: Good performance back again

This phenomenon was repeatable on all tests that I performed, and it does not depend on the analog input tone's frequency. I mean, I tested many different frequencies between 10 MHz and 800 MHz with the same results: whenever the sampling rate was between 1700 - 1800 MHz, interleaving images suppression decreased significantly. I even tried to vary the frequency of the input tone so that the digital frequency of the sampled signals (i.e. the frequency in rad) was the same on all cases, but again, depending on the sampling rate I got better or worse interleaving spurs suppression. If somebody is interested in seeing the rest of the captures I made -maybe for a comparison- I can upload them, just tell me. There are quite a few.

I would like to know if this phenomenon is normal, or if I could be messing the setup somehow, since the converter's specifications are given for sampling rates of 3GHz (or something like that) on the datasheets. About my setup and setup proceure:

- HW and SW: ADC32RF45EVM rev D + TSW14J56EVM rev B, HSDC Pro v4.2 and ADC32RF45 EVM 2.1, both running on Windows 10.

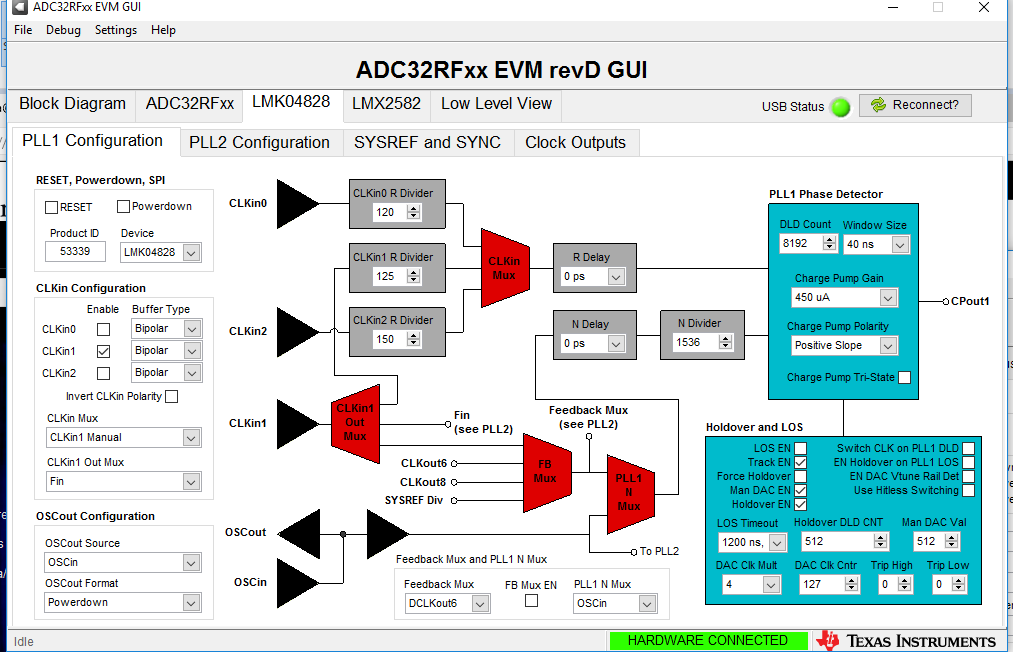

- The EVM is configured as indicated in the ADC32RF45 User Guide. Config files are LMK_ADC32RF45_LMF_82820_ExtClock.cfg and ADC32RF4x_12bit_LMFS_82820.cfg, written in that order after a reset on the LMK, and with an intermediate hard reset on the ADC.

- I'm using a single clock source to provide the ADC's clock and the LMK04828's reference by means of an splitter. The generator is adjusted so that power is about 7dBm at the EVM's SMA connectors. The clock is BP-filtered to suppress any harmonics.

- Power consumption is about 1.3A before configuring the LMK and ADC, and about 1.8A afterwards. Power supply is limitted to 4A and the current limitter stays off all the time.

- The analog signal is synthesized by means of a second signal generator and some BP or LP filters depending on the tests; input power is about 2-3dBm at the SMA connector.

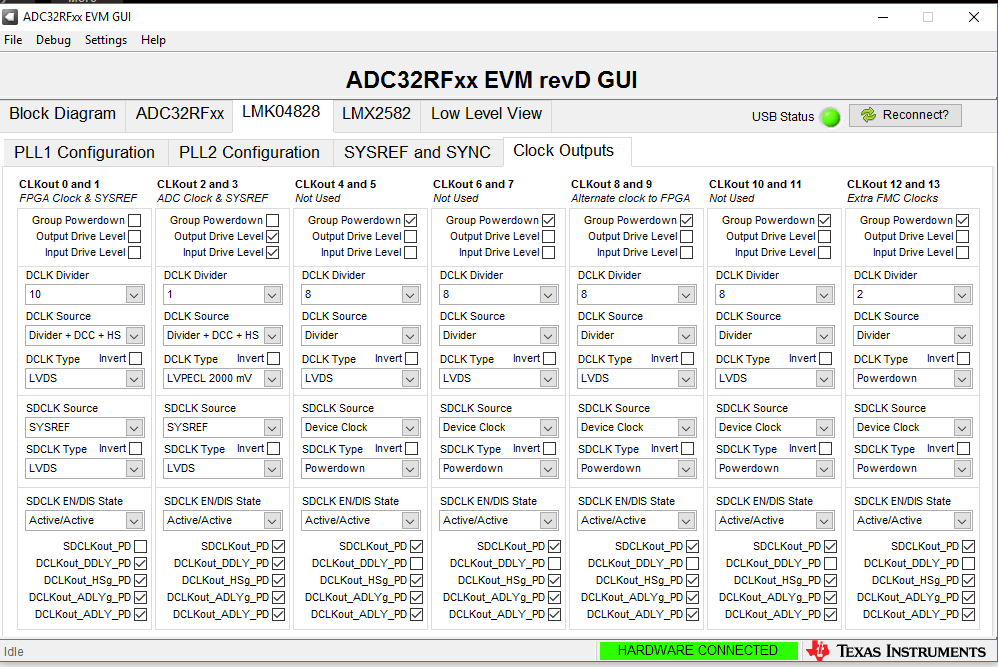

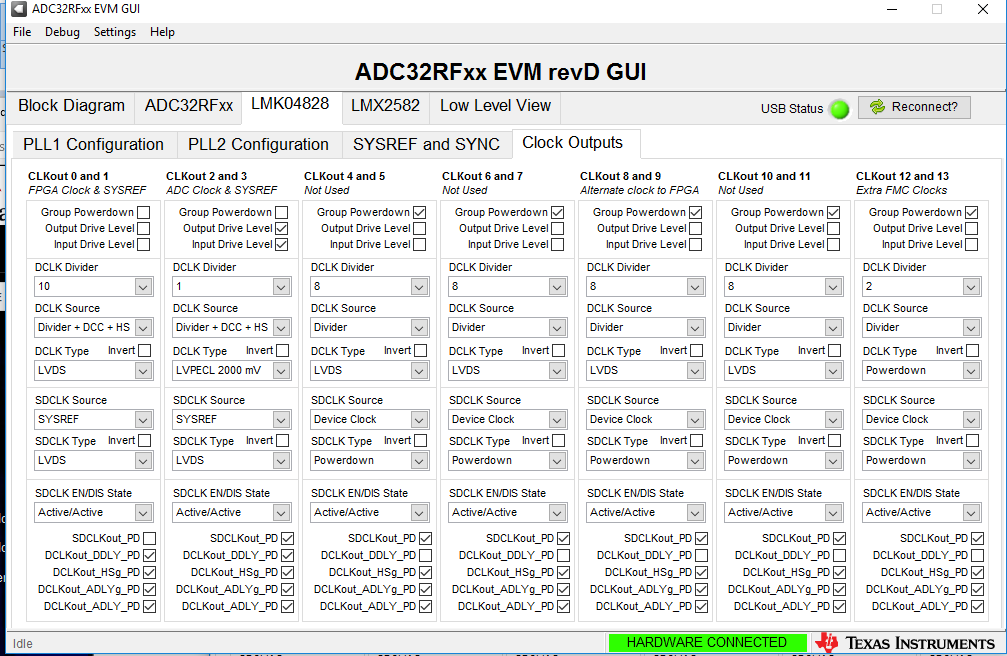

Some captures of the EVM software showing ADC and LMK configuration:

The "Slow speed En" was adjusted depending on the actual sampling rate (< 1.75 GHz for 1600 and 1700 MSPS) with no impact on the results.

LMK04828:

Two more things before I finish:

- I have noticed a strange thing on the TSW14J56EVM: according to the user guide (SLWU086C), LED D3 indicates that the ADC is synchronized with the JESD204B receiver on the FPGA side when it is OFF, but in my case this led stays ON excepting for a few tenths of a second every time I perform a capture. Data appears to be all right, but I do not know if this is a symptom of something not going 100% well. LEDs 2 and 4 blink at a few Hz as indicated on the previous document.

- I have noticed as well the Fs/8 notches of the interleaving correction block (this is explained in this post) when I inject tones at the input. My question is: the "filters" that Mr Richard Prentice indicates on the previous post are always there? I mean, if I sample, say, a 6 MHz wide QAM signal centered at Fs/8 for a given Fs, will this filtering effect obliterate my signal?

Anyway, I would really appreciate any information regarding these questions or the issue I have with performance and sampling rates.

Thank you very much in advance and sorry for the long post.

B.R.

Pablo.