I need to interface ADS8860 with an FPGA using SPI - 3 wire operation.

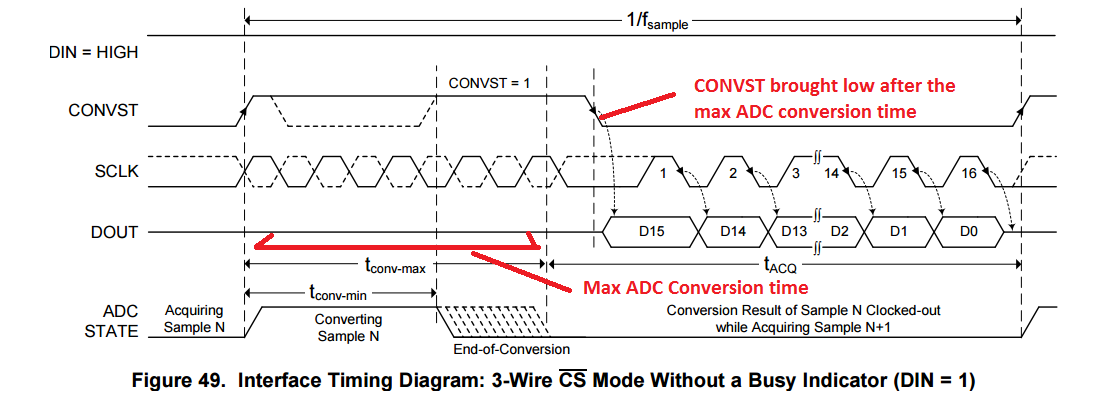

According to the timing diagram, the CONVST pin must not be held high more than 710ns. I would like to know whether holding it longer will produce incorrect results.

As far as I understood, the CONVST pin holds the data as long as it is high and starts conversion process at the falling edge of the CONVST signal. In principle, holding the CONVST pin high for a longer time than 710ns should only hold the input data longer.

Have I understood the concept correctly?

Thanks

Tobie