Hi,

I am using ADS1298 with a development kit having android running on it. I am interfacing ADS1298 with the kit through SPI connections on J3. I ma using only three channels. CH1,CH2 and CH3, Channel's Mux is set to internal test signals. Here is some screen shots that shows my register settings and outputs :both while using Evaluation board and and while using kit.

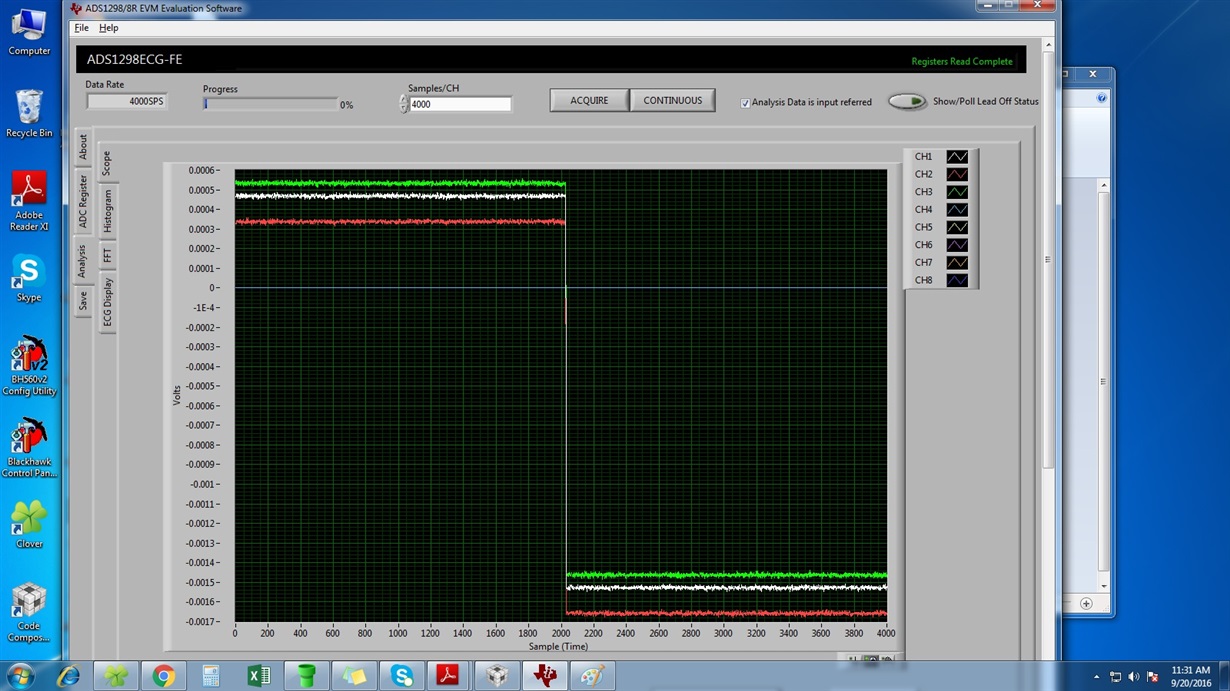

Kit's Output

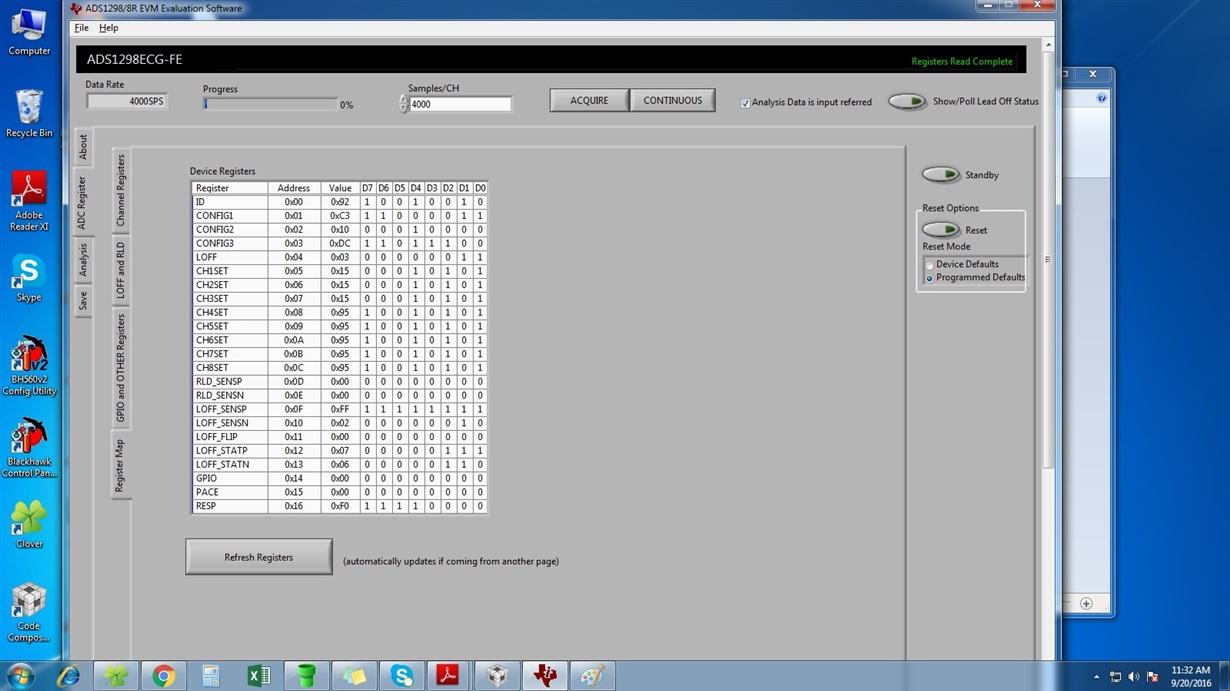

Register Settings

EVM's Output

As it is seen, with data rate = 4000SPS and acquiring 4000 Samples/Channel , I get only one pulse with EVM and Multiple pulses with the kit. Can anyone help why is this happening ?

Register configurations are same in both cases. Difference is the SCLK frequency. With kit SCLK is 1 MHz and with EVM the clock is approx 15 MHz.