Other Parts Discussed in Thread: ADS8353

Hi,

My customer is using ADS8353.

ADS8353 is operated with MSP430.

Customer has a question about Serial interface timing.

ADS8353 data width is 16bit.

But MSP430 data width is 8 bit, then MSP430 need to reciave data 2 times from A/D .

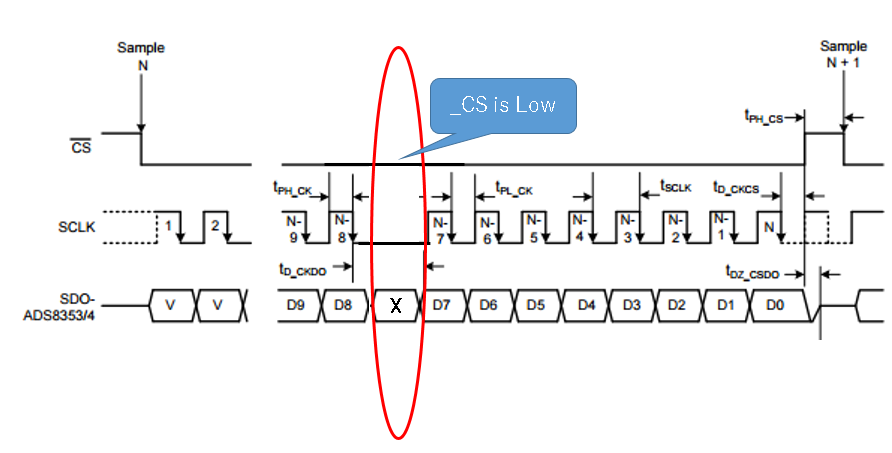

For the reason, Serial interface waveform is below.

There is a time between 8bits SCLK and 8bits SCLK.

Is it problem the following timing?

Best regards,

Shimizu