Hello,

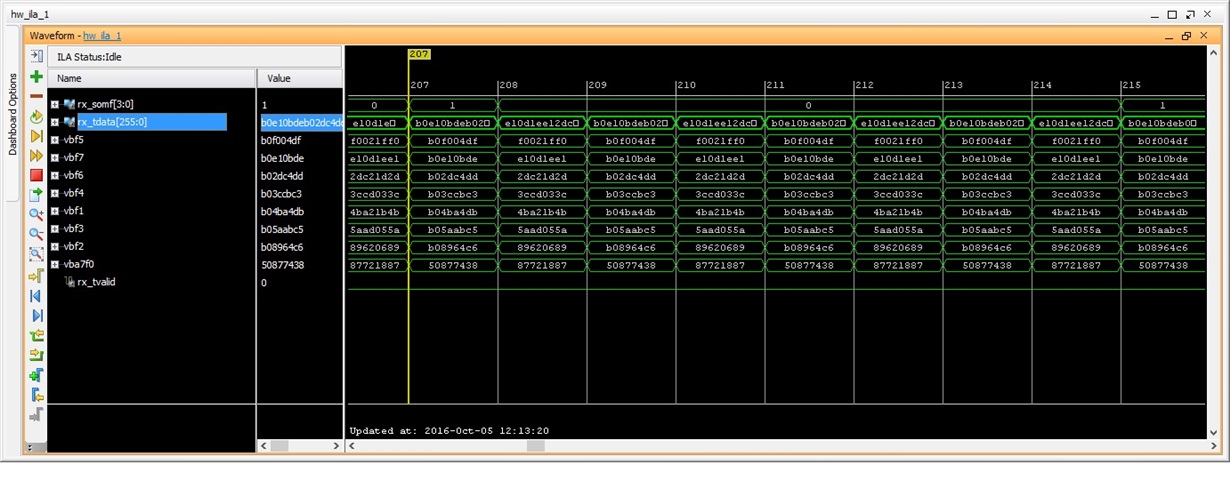

I am using ADC12J4000 with Xilinx platform. I am able to achieve sync and retrieve data, but the data shows harmonics (no scrambler). I am configuring ADC with 2.7Gsps with DDR bypass mode.

I also see that with scrambler on the data is absolutely bad. I am not sure whether I can blame it on Xilinx FPGA.

However, I have verified that the board works fine with 14J56revD Board when I use HS Data converter Pro software. (It uses LMK4828 reg 0x110= 0xA, while on Xilinx board I have to program 0x05)

I am not sure what could be wrong. The Xilinx board works fine with other ADC eval platforms.

Appreciate any help in advance.

D