We are using DAC38j82 to perform waveform generation in the band of 20 - 500 MHz and sampling at 1.2 GHz.Required SFDR and harmonic suppresion for our application is 60 dBc.During initial testing in the above mentioned band we are able achieve the specfications , until outputs were generated in following manner

- For 200.354 MHz - SFDR and harmonic suppression > 60 dB.

- For 200.001 MHz - suppression is below 50 dB.

four parallel DDS sampling at 300 MHz is implemented to meet the sampling rate of 1.2 GSPS.

Kindly provide insights on these whether issue location is at DDS or at DAC.

Also these spurious levels are only high at specfic points such as 40.001 MHz,80.001MHz,120.001MHz,160.001MHz,200.001 MHz,240.001MHz,280.001 MHz......440.001MHz & 480.001 MHz.

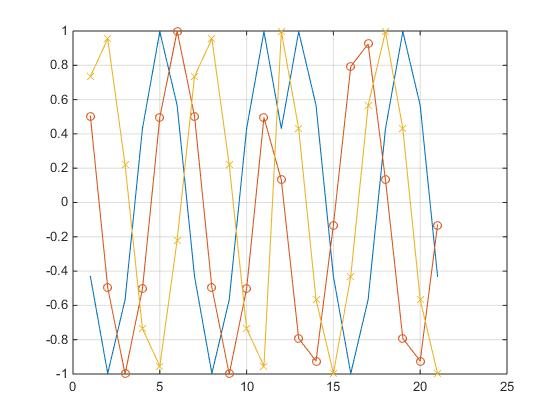

Below is the output spectrum at 240.001 MHz

Below is the spectrum for the 200.001 MHz.