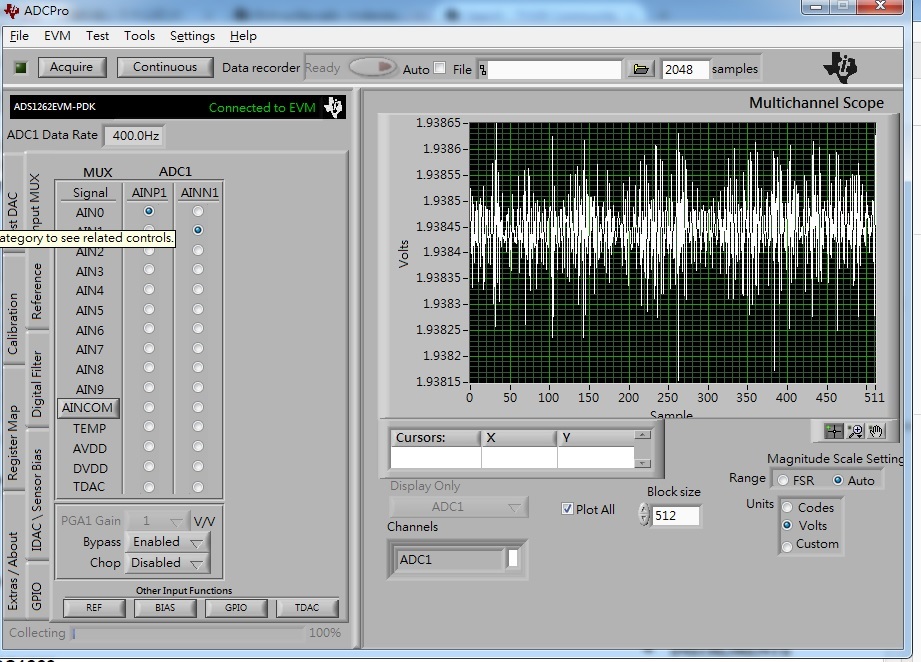

I try to use ADS1262EVm to measure a voltage (2V) from power supply with INP0 (1.9xxV) & INP1 (0V)

From this post

There are a few actions you can take to make sure that you don’t violate the PGA’s input range requirements:

1. Level shifting

2. Bipolar supplies

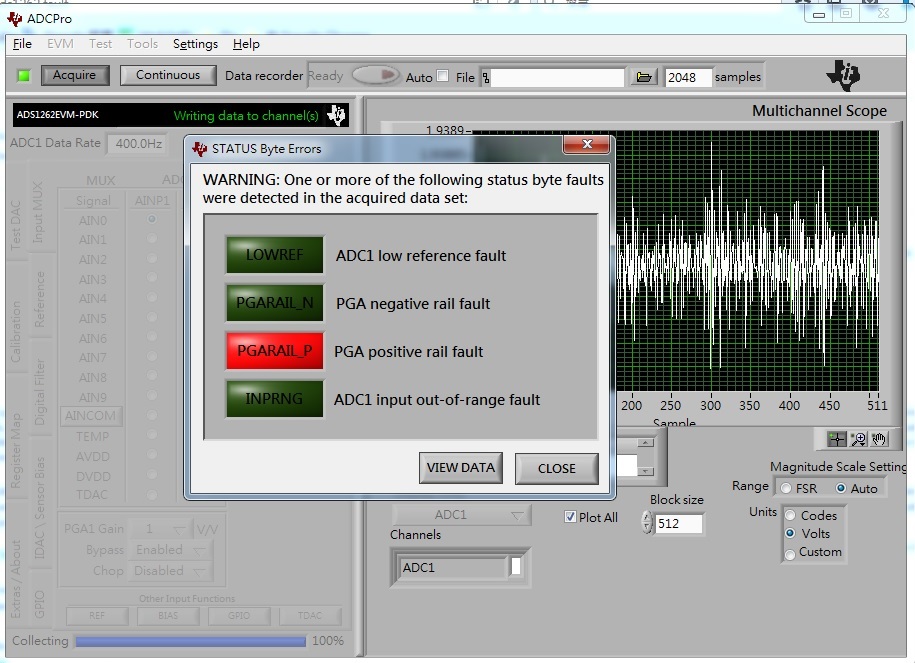

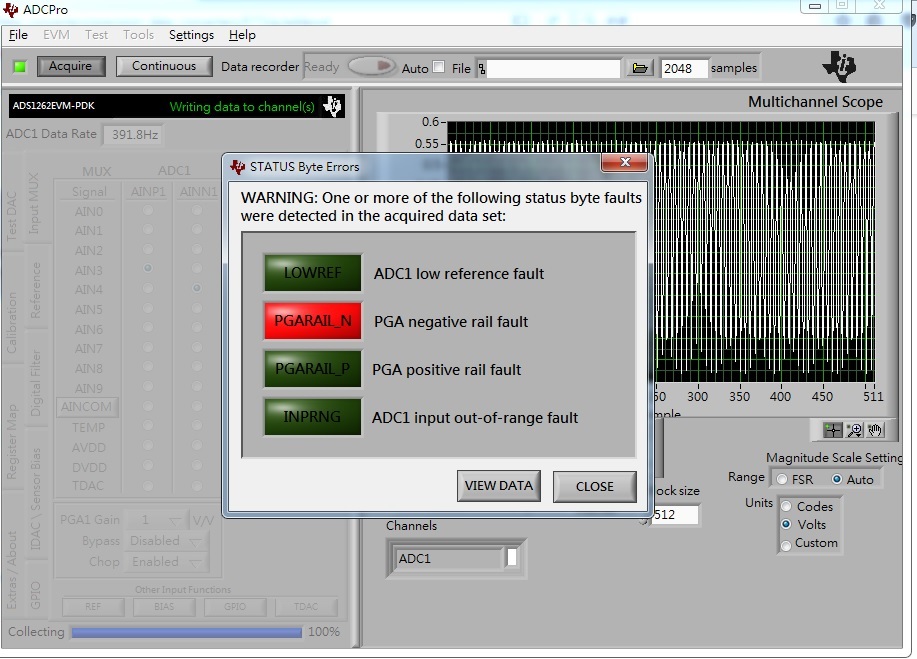

3. Bypass the PGA

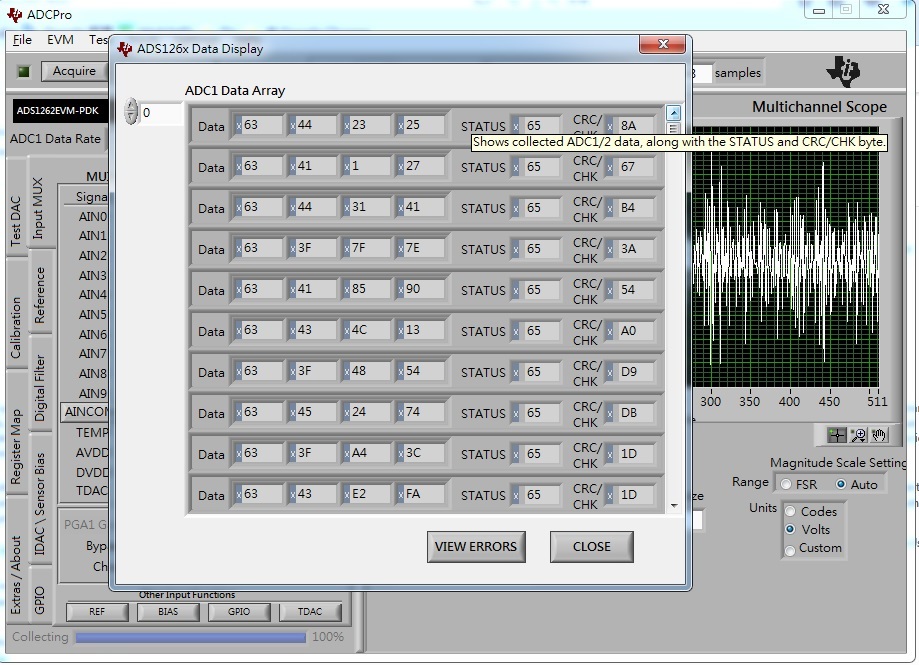

Thus, I bypass PGA, but the PGARAIL_FAULT still occur. Why? The results seems to be okay, but the warning continues to pops out.