Hello,

Our customer use the ADS7841.

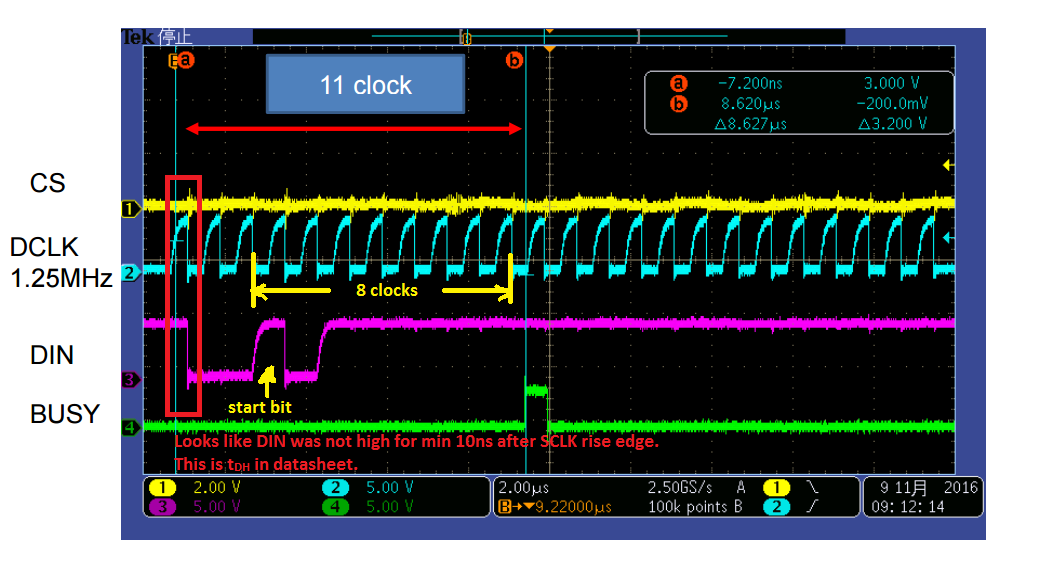

The BUSY pulse occur at after 8 clocks.

In sometime, it occur at after 11 clocks.

Is it correct?

The configuration of the customer as follows.

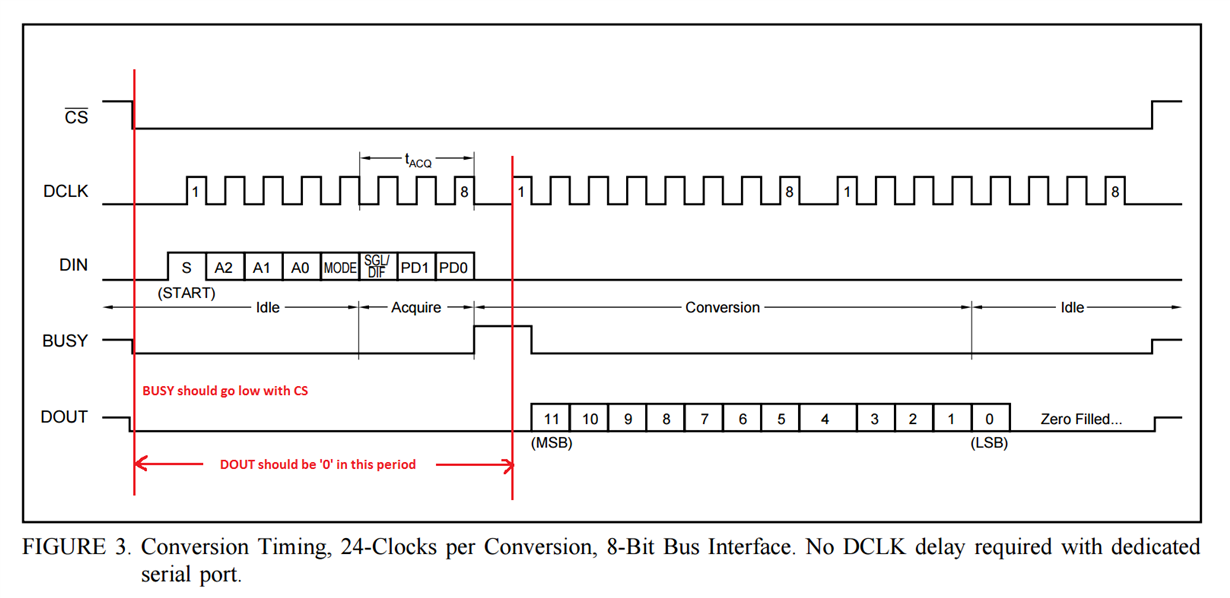

12bit conversion mode

24clocks per conversion

Best Regards,

Naoki Aoyama