Dear Community Users,

I am trying to read out data out of the ADS1271 24-Bit Delta Sigma Converter. As micro controller board I am using the STM32F429 Discovery Kit. I am generating the ADS1271 Master Clock, so called CLK in the data sheet, via the Master Clock Output (MCO) Pin of the STM32F429 Board. For this, I changed the PLL settings so, that my Board is running at 108MHz. On the MCO I am using a prescaler of 4, so I getting the desired 27MHz. To check the frequency, I am using the "Open Bench Logic Sniffer (Logic Analyzer). Test result: 27,004MHz, Duty Cylce=52,4%. The datasheed says: for optimum performance the ratio of SCLK and CLK should be 1/2,1/4.... (Page: 25, Datasheet) For the SCLK of the SPI I used a Prescaler of 4. The clock source of SCLK is the APB2 Clock, which is derived from the system clock core of 108MHz. With a prescaler of 4, i got for the SCLK a clock of 13.5MHz. So my ratio is: 1/8. So far so good.

At the moment I am reading the data like this:

.....

while(1)

{

if(GPIO_ReadInputDataBit(DRDY_PORT,DRDY_PIN)==0){

SPI_Cmd(SPI4,ENABLE);

SPI4_send(0xAA); //First Byte

SPI4_send(0xAA); //Second Byte

SPI4_send(0xAA); //Third Byte

SPI_Cmd(SPI4,DISABLE);

delay_us(2);

//}

}

...

Two explanations:

1.) I just send dummy DATA to the ADS1271 with the STM32F429, the DOUT is checked via the Logic Analyzer, so don't wonder why I don't read it in main

2.) In the datasheet it says: after data retrieval held SCLK low (Page: 25, Datasheet)

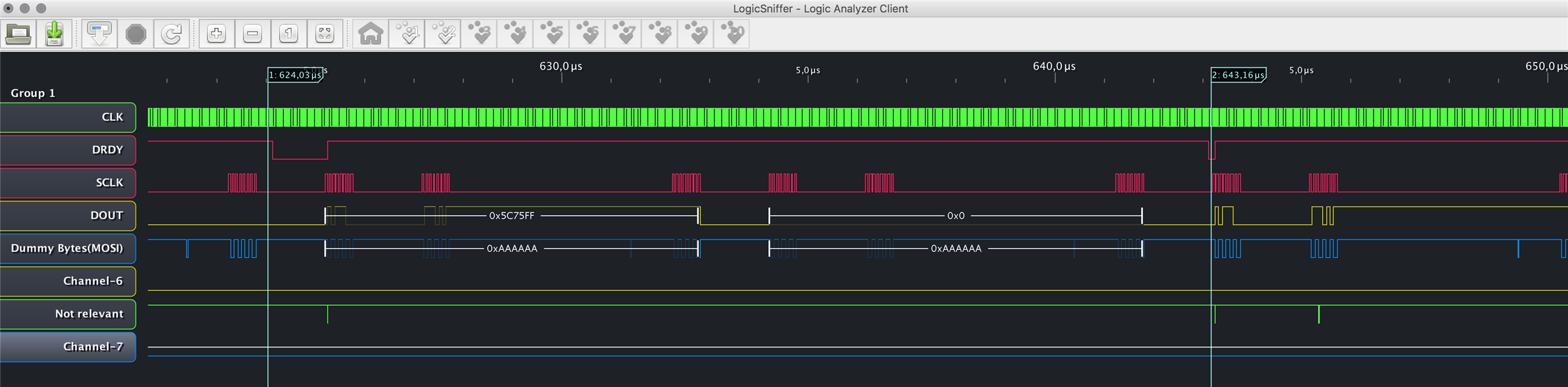

If i don't read any data, I am seeing on my Logic Analyzer the same "plot" like Figure 63. The frequency of the !DRDY is varying between 52,734kHz and 52,715kHz.

My question: do I have to wait in the while loop in the main until !DRDY gets High or Low ? I found an example code in the internet, where someone is waiting until !DRDY gets High. When I wait !DRDY getting High, I just receive Figure 63. When I wait for !DRDY getting low I get Samples but I have recognized, that !DRDY is changing his state way before the first Sample is read out. I just posted a screenshot. In this example I just checked one sample out, which leads to "0x5C75FF". In Decimal 6059519. When I convert it with the following equation: v_measured=adc_val/(res/v_ref)=6059519/(2^23-1/2.49V) (two's-compliment 24Bit). The result is 1.804V. So this looks correct, because I tied AIN- to GND and AIN+ to 1.8V.

Datasheet Link: www.ti.com/.../ads1271.pdf

At the moment I am confused, if I am doing right things or not :P.

Please apologise my bad english.

I am thankfully for every hint.

Best regards,

tugrul