Hello,

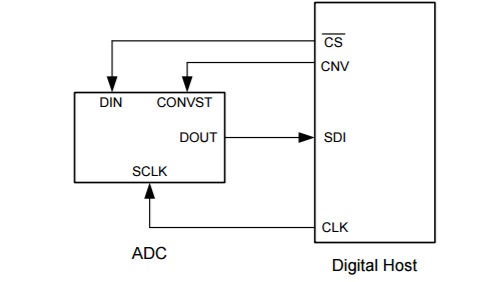

We're evaluating the ADS8881 on the ADS8885 EVM without the MMB0. We've evaluated the device in both the four wire configuration and three wire configuration, and in both see unexpected output.

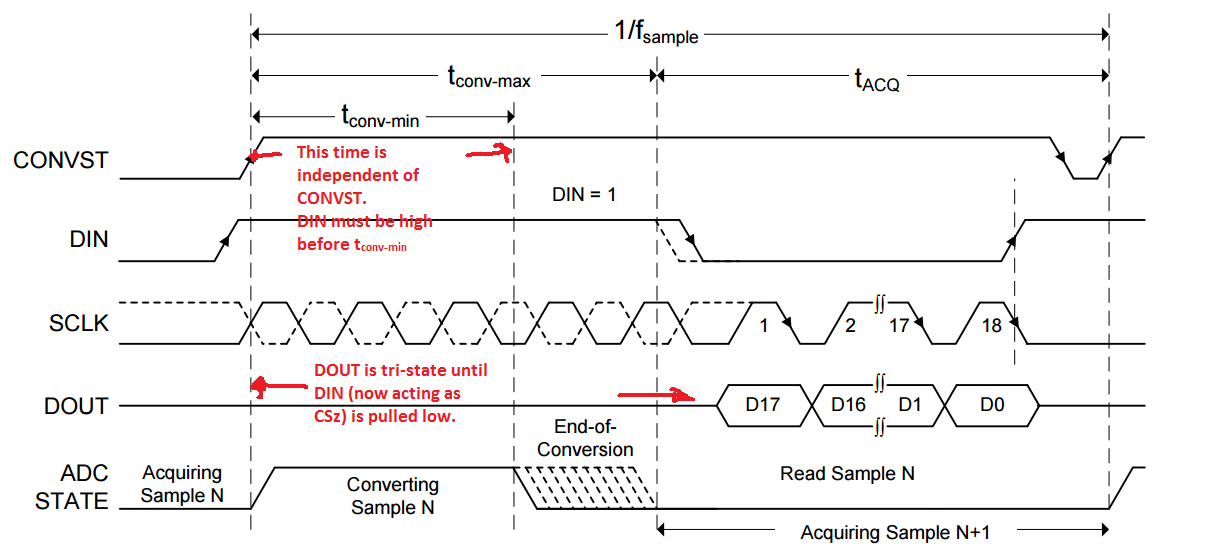

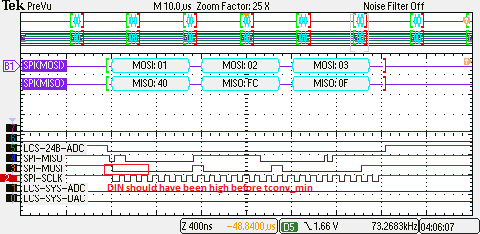

The four wire mode, pictured below, shows a MISO LSByte of 0x0F--the very lowest for this 18bit A/D should be 0x3F, correct? (please note, we aren't actually sending 1,2,and 3 on MOSI, it's more for debug purposes.)

I see the same behavior with 3-wire configuration:

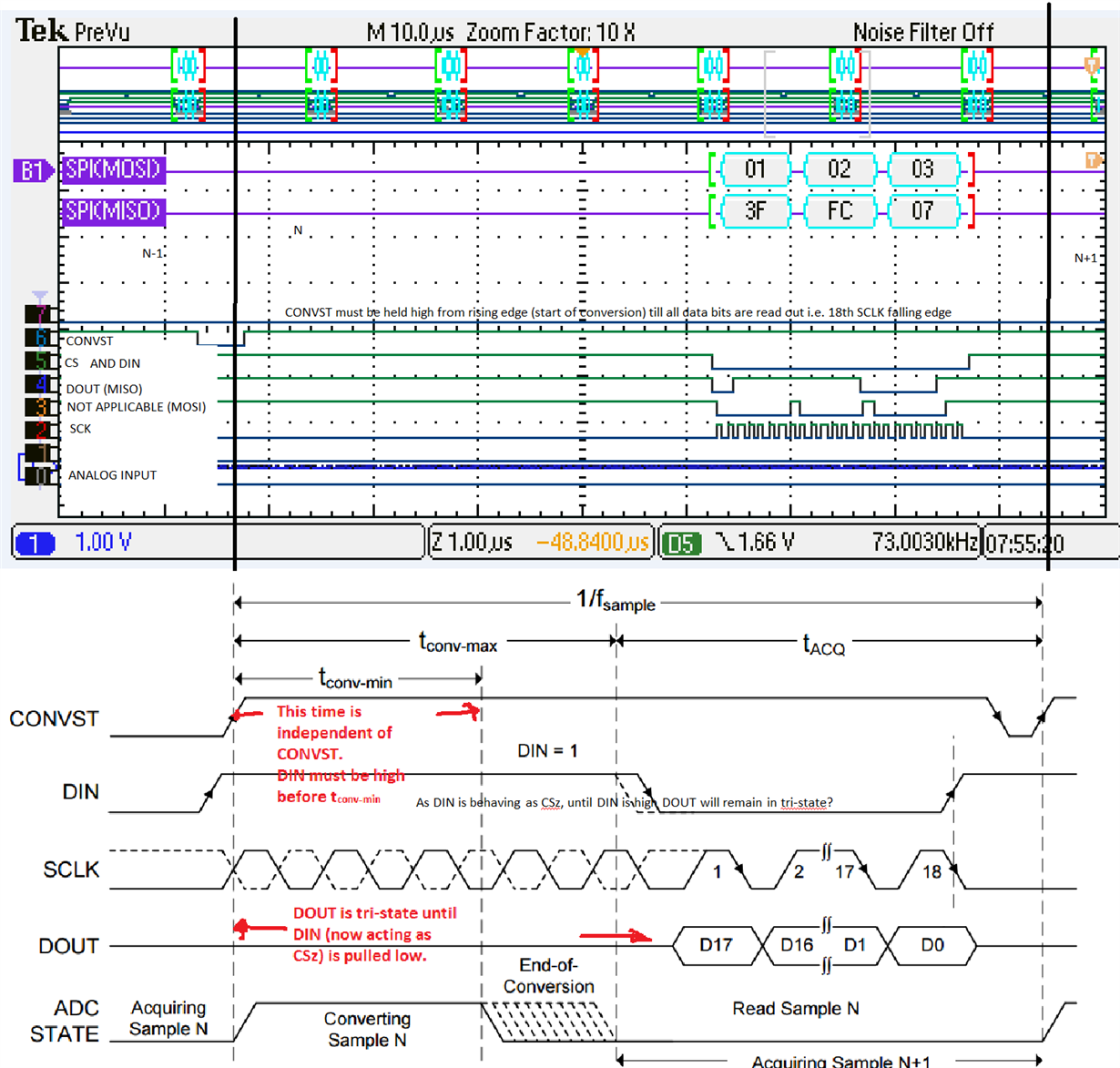

This other scope shot fits the datasheet description for four-wire operation exactly, with an extremely long conversion time, but the values are still strange. In the above shot, CONVST is channel 6, and the large gap is a generous conversion time.

"In this interface option, DIN is controlled by the digital host and functions as CS. As shown in Figure 55, with DIN high, a CONVST rising edge selects CS mode, forces DOUT to 3-state, samples the input signal, and causes the device to enter a conversion phase. In this interface option, CONVST must be held at a high level from the start of the conversion until all data bits are read. Conversion is done with the internal clock and continues regardless of the state of DIN. As a result, DIN (functioning as CS) can be pulled low to select other devices on the board. However, DIN must be pulled high before the minimum conversion time (tconv-min) elapses and remains high until the maximum possible conversion time (tconv-max) elapses"

am I misinterpreting the datasheet? Is Din tristate only for the conversion phase regardless of CONVST? Should the second scope capture give the proper readout? Probably missing something glaringly obvious here, thank you for your help!