- Can you share FPGA firmware of EVM to united image? They want to build their own system.

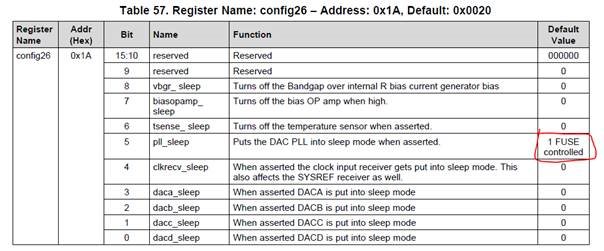

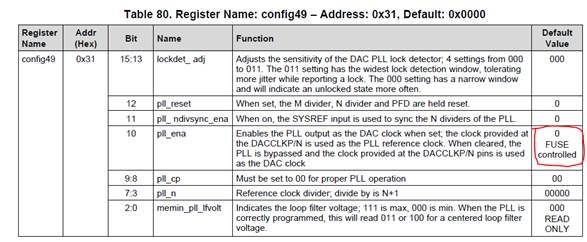

- FUSE controlled, what’s meaning of the 1 fuse controlled? Does 1 mean enter sleep mode and 0 mean go out of sleep mode? Can it be read and written? Can this bit be written one time or many times?

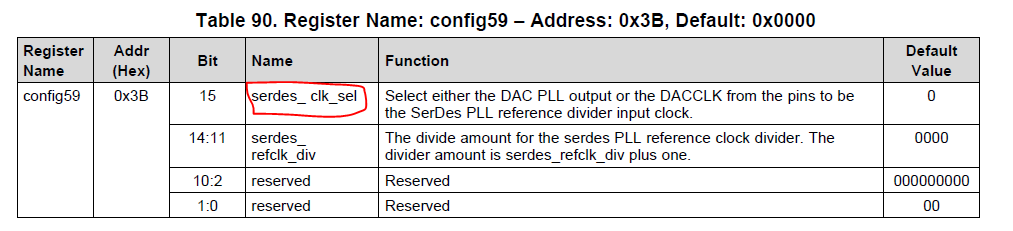

- Table 90 in datasheet, serdes_ clk_sel, set this bit 0 to choose DACPLL or DACCLK from the pins?