Other Parts Discussed in Thread: REF3325, , OPA320, OPA625, OPA314, OPA192

Hello

Intro:

i am designing a board that will have 11 photo-diodes (PD). The PD are connected to transimpedance amplifier (TIA) and the output of TIA is routed to ADS7952 (ADC). The ADC is configured to run in manual mode with 1MHz as spi clock. The read is preformed every 16.66ms and all channels are read from 0-11. I have chosen REF3325 as my 2.5V ref voltage. I have routed the ADC in buffered mode ... with MUX directly connected to AINP.

Problem:

When i read all the channels i can see that CH8 is extremely noisy and it has an offset. Even if i apply a constant voltage to all channels i can notice that CH8 shows much lower value. I can not explain my self why. In datasheet i didn't find anything that can explain this behavior of CH8.

Additional Info:

As TIA i am using OPA314. I tried changing for OPA320 and OPA625. OPA625 showed the best performance but there was still a fair amount of noise and offset on CH8. I tried using LTC6268. At this point noise and offset were gone. But LTC6268 has 16mA power consumption and with 11PD that is close to 200mA. That is outside of my power budget?

Question:

Is there anything special about CH8 that it shows this type of behavior?

If i would to use ADC with buffer between MUX and AINP would the problem go away?

With buffered implementation do i still need 150p cap on each channel?

My board has 3.3V power supply. That means i can not use OPA192 as V-buffer. Can you maybe suggest V-buffer that works at 3.3V and can be used with ADS7952?

Scope Pictures:

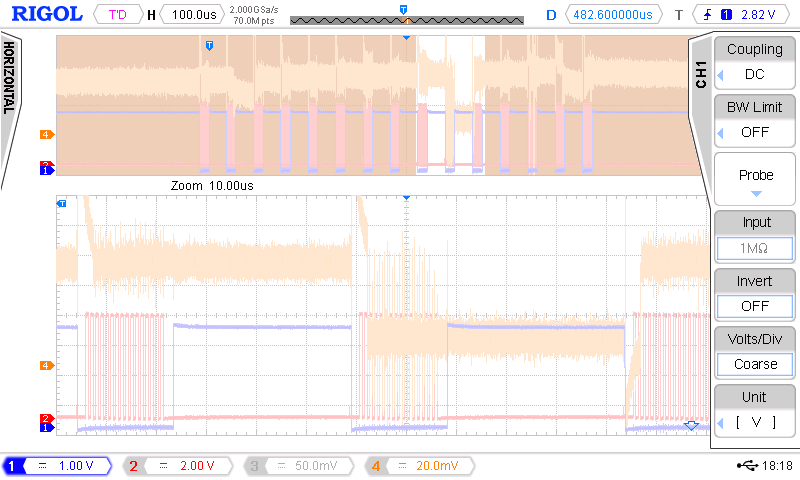

I did some measurements of the board with my scope. I synchronized my acquisition with SSn (purple line). Red line presents the SCK and yellow line is the signal between MUX and AINP.

As you can see on the yellow line there is much higher noise on 10th SSn low. Interesting is to see that there is no voltage drop which one would expect when ADC shows a offset in the readout.

Next picture present the zoom on the noisy channel

As you can see the yellow line (signal between MUX and AINP) spikes on each transition of the SCK ( red line ). When i compare this to acquisition just before i see no spiking or flickering of the measured signal ( yellow line ). Please see the next picture.

This is zoomed acquisition just one channel before. As you can see there is no noise.

I also acquired SPI signals with my scope. Figure Below:

I have zoomed on the 3 acquisitions. I want to show how we are addressing the ADS7952. As you can see from MOSI the channel count is progressing from one measurement to an other. Also MISO shows that ADS7952 is giving us results in progression (first 4 bits of MISO increment correctly). On the last measurement is where i would see the troubled MUX-to-AINP signal.

Thank you very much for your help

Schematic Pictures:

Top level file of my board

Trans-impedance amplifier

ADS7952