We have designed a platform in which DAC3484 is interfaced with xilinx FPGA through FMC-HPC. Here, we tried giving 7MHz sine wave to all four four channels (I0 Q0 I1 Q1) generated from DDS in FPGA at 153.6MSPS rate.

The DACDATA_CLK is 307.2 and DAC_CLK is 614.4 (interpolation by 4). the DAC NCO is configured for 192MHz. FRAME signal has used for syncing source for FIFO. and NCO sync source is SIFSYNC.

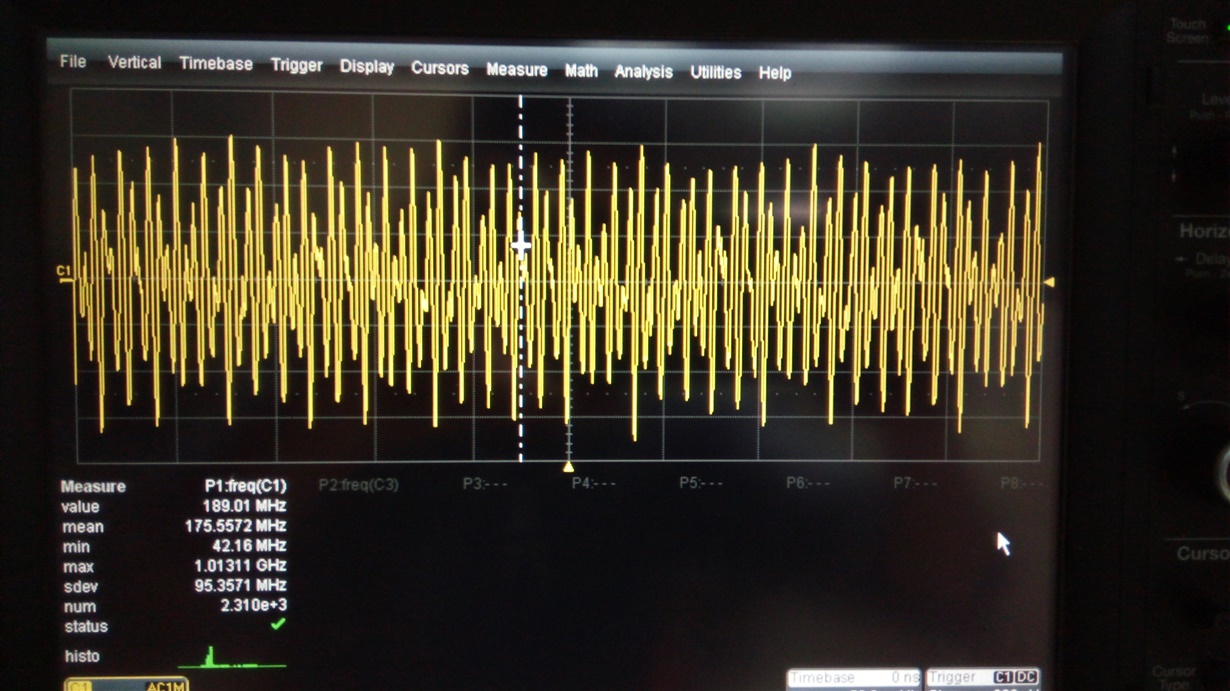

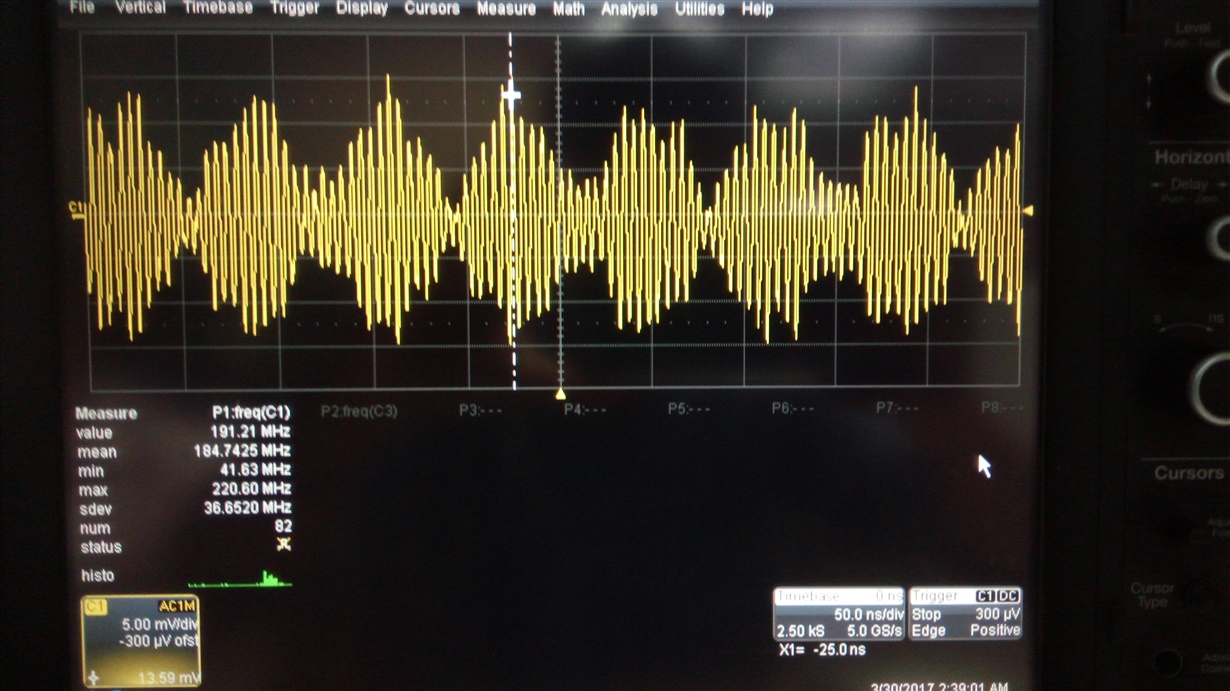

but we had observed that there are two harmonics at 199MHz (192+7) and 185MHz (192-7) on the DAC output of channel C-D and 199MHZ on channel A-B.

what could be reason for such behavior ?

The reguster setting is given below,

Cw0 <= x"00_028F";

Cw1 <= x"01_0100";

Cw2 <= x"02_80D2"; -- mixer gain disabled

Cw3 <= x"03_D000";

Cw4 <= x"04_0000";

Cw5 <= x"05_0000";

Cw6 <= x"06_3300";

Cw7 <= x"07_FFFF";

Cw8 <= x"08_0000";

Cw9 <= x"09_8000";

Cw10 <= x"0A_0000";

Cw11 <= x"0B_0000";

Cw12 <= x"0C_0400";

Cw13 <= x"0D_0400";

Cw14 <= x"0E_0400";

Cw15 <= x"0F_0400";

Cw16 <= x"10_0000";

Cw17 <= x"11_0000";

Cw18 <= x"12_0000";

Cw19 <= x"13_0000";

Cw20 <= x"14_0000";--- reg 0x14-0x17 IF=192MHz

Cw21 <= x"15_5000";

Cw22 <= x"16_0000";

Cw23 <= x"17_5000";

Cw24 <= x"18_2000";

Cw25 <= x"19_0000";

Cw26 <= x"1A_0020";

Cw27 <= x"1B_0800";

Cw28 <= x"1C_0000";

Cw29 <= x"1D_0000";

Cw30 <= x"1E_1111";

Cw31 <= x"1F_8880";

Cw32 <= x"20_2201";

Cw34 <= x"22_1B1B";

Cw35 <= x"23_FFFF";

Cw36 <= x"24_1800";

Cw37 <= x"25_7A7A";

Cw38 <= x"26_B6B6";

Cw39 <= x"27_EAEA";

Cw40 <= x"28_4545";

Cw41 <= x"29_1A1A";

Cw42 <= x"2A_1616";

Cw43 <= x"2B_AAAA";

Cw44 <= x"2C_C6C6";

Cw45 <= x"2D_0004";-

Cw46 <= x"2E_0000";

Cw47 <= x"2F_0000";

Cw48 <= x"30_7FFF";